ECTC: 3-D IC Hybrid Bonding Developments

# pcdandf.com July 2022 DESIGN & FAB Sector A Control of Control of

# BREAKING NEWS

## CURRENT EVENTS -

## **Design Charts for Sizing Electrical Traces**

SPS ARE NOT ALL THE SAME

PACKING YOUR PCBS

CONTROLLING IMPEDANCE

This issue of Printed Circuit Design & FAB/Circuits Assembly is brought to you by:

Conference & Exhibition

## The Largest Conference and Exhibition for Printed Circuit Board Design, Fabrication and Assembly in the Silicon Valley

## CONFERENCE: October 4 – 7 EXHIBITION: Wednesday, October 5

## SANTA CLARA CONVENTION CENTER, CA

## **REGISTER NOW**

## **SPEAKERS**

- ≫ Dan Beeker

- ≫ Tomas Chester

- ≫ Keven Coates

- $\gg$  Rick Hartley

- ≫ Susy Webb

## HOT TOPICS

- $\gg$  Controlling noise

- $\gg$  Design for resiliency

- ≫ IoT design

- ≫ RF/microwave design

- ≫ Stackups

## HIGHLIGHTS

- $\gg$  40 presentations + 9 Free

- $\gg$  110+ Training hours

- $\gg$  Professional Development Certificate

- $\gg$  100+ exhibiting companies

- $\gg$  lunch & reception on exhibition floor

## PCBWEST.COM

# **CONSULT WITH FUJI FOR FREE**

The Fuji America Tech Center is the #1 place for <u>any</u> manufacturer to get free consultations on:

- Machine Testing

- Process Development

- Software Applications

- Vision Development

- Machine Customization

...And much more!

## SCHEDULE YOUR VISIT TODAY CALL 847-913-0162

## **PROTOTYPES** FROM TAIWAN

# No Tariffs!

## Best Quality and Price!

## Technology:

Up to 50 Layers Any Layer HDI Sequential Lamination Blind / Buried Vias Laser Drilling / Routing Heavy Copper

## Materials:

Fr4 Metal Core Isola Rogers Polyimide - Flex Magtron

www.PCB4u.com sales@PCB4u.com Tel: (408) 748-9600 2986 Scott Blvd., Santa Clara, CA 95054 SAM & ITAR Registered UL E333047 ISO 9001 - 2015

#### FIRST PERSON

6 THE ROUTE Staff retention.

Mike Buetow

#### MONEY MATTERS

#### 18 ROI

Enabling (disruptive) tech. Peter Bigelow

19 BOARD BUYING

Perfect packaging. Greg Papandrew

#### TECH TALK

#### 22 ON THE FOREFRONT

More chips per panel. E. Jan Vardaman

#### 28 DESIGNER'S NOTEBOOK

Specifying impedance. John Burkhert, Jr.

#### 46 GETTING LEAN

Industry 4.0 AOI. Filemon Sagrero

#### 47 SEEING IS BELIEVING

Swindlers' lists. Robert Boguski

#### 53 TECHNICAL ABSTRACTS

#### DEPARTMENTS

#### 8 AROUND THE WORLD

- 16 MARKET WATCH

- 50 OFF THE SHELF

## PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

#### FEATURES

37

#### 31 TRACE HEATING *cover story*

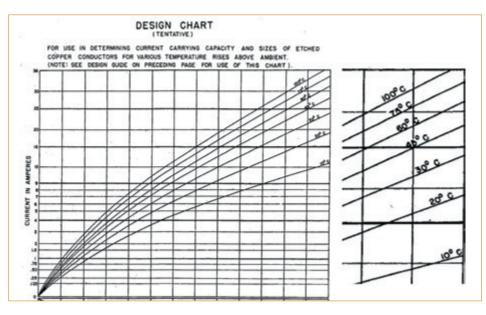

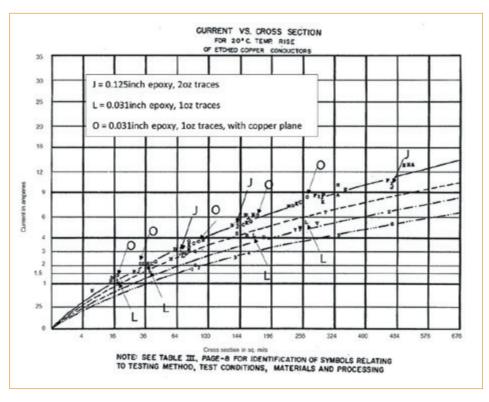

#### Making Technology-Specific Design Charts

Companies should perform their own testing or develop their own thermal models to determine conductor current carrying capacity in any given technology. An explanation of IPC-2152 and the information it provides to get started. by MIKE JOUPPI

#### **OSP Myths Dispelled**

After many years of debate, a specification for organic solderability preservatives is finally here. IPC-4555 sets the record straight: OSPs are not all the same, and they have regained their leadership role as a final finish. by MICHAEL CARANO

#### 41 ACQUISITIONS

#### A Royal Summit

In May, Summit Interconnect announced its acquisition of Royal Circuit Solutions, expanding the fabricator's capacity of rigid and flex PCBs. But it was the behind-thescenes technologies and assembly capacity that convinced Summit president and CEO Shane Whiteside to make the deal. by MIKE BUETOW

BREAKIN

**Design Charts for Sizing Electrical Inace**

Othe Are Nor As the Dee

lakes Har Add

Downsparse Jumpoint

CURRENT EVENTS -

#### ON PCB CHAT (pcbchat.com)

RIT PCB DESIGN COURSE RECAP with DR. KIRSCH MACKEY and DR. JAMES LEE

## BEST PRACTICES FOR PURCHASING X-RAY EQUIPMENT

with KEITH BRYANT, DR. DAVID BERNARD, DAVID KRUIDHOF and ROBERT BOGUSKI

#### **PEOPLE MANAGEMENT SKILLS**

with JOHN BURKHERT JR.

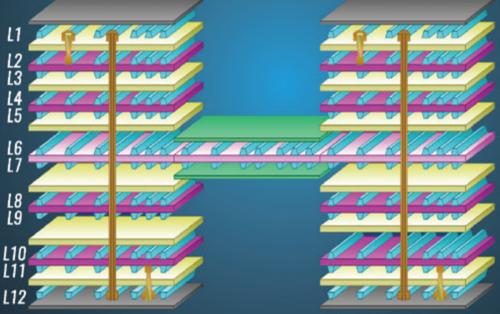

## Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

## When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

## Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

PCEA

PO BOX 807 AMESBURY, MA 01913

#### PCEA BOARD OF DIRECTORS

Stephen Chavez, CHAIRMAN Michael Creeden, VICE CHAIRMAN Justin Fleming, SECRETARY Gary Ferrari, CHAIRMAN EMERITUS

#### MEMBERS

Michael Buetow Tomas Chester Douglas Dixon Tara Dunn Richard Hartley Scott McCurdy Anaya Vardya Susy Webb Eriko Yamato

#### PCEA.NET

#### THE PRINTED CIRCUIT ENGINEERING ASSOCIATION, INC. BRANDS:

#### PUBLICATION

| PCD&F/Circuits Assembly                                    | digital.pcea.net |

|------------------------------------------------------------|------------------|

| WEBSITES<br>PCD&F<br>Circuits Assembly                     |                  |

| NEWSLETTER<br>PCB Update                                   | pcbupdate.com    |

| PODCASTS<br>PCB Chat                                       | pcbchat.com      |

| EVENTS<br>PCB West<br>PCB East                             |                  |

| EDUCATION<br>PCB2Dayprinted Circuit Universityp            |                  |

| AWARDS PROGRAMS<br>Service Excellence Awards<br>NPI Awards | ,                |

| DATABASE                                                   | poddiananoom     |

Directory of EMS Companies.....circuitsassembly.com

PRINTED CIRCUIT DESIGN & FAB pcdandf.com circuitsassembly.com

#### STAFF

PRESIDENT

Mike Buetow 617-327-4702 | mike@pcea.net VICE PRESIDENT, SALES & MARKETING

Frances Stewart 678-817-1286 | frances@pcea.net SENIOR SALES EXECUTIVE

Brooke Anglin 404-316-9018 | brooke@pcea.net CHIEF CONTENT OFFICER

Chelsey Drysdale 949-295-3109 | chelsey@pcea.net

#### PCD&F/CIRCUITS ASSEMBLY EDITORIAL

CHIEF CONTENT OFFICER

Chelsey Drysdale 949-295-3109 | chelsey@pcea.net

#### **COLUMNISTS AND ADVISORS**

Clive Ashmore, Peter Bigelow, Robert Boguski, John D. Borneman, John Burkhert, Jr., Joseph Fama, Mark Finstad, Bill Hargin, Nick Koop, Alun Morgan, Susan Mucha, Greg Papandrew, Akber Roy, Chrys Shea, Jan Vardaman, Ranko Vujosevic, Gene Weiner

#### PRODUCTION

ART DIRECTOR & PRODUCTION blueprint4MARKETING, Inc. | production@pcea.net

#### SALES

VICE PRESIDENT, SALES & MARKETING Frances Stewart 678-817-1286 | frances@pcea.net SENIOR SALES EXECUTIVE Brooke Anglin 404-316-9018 | brooke@pcea.net

#### REPRINTS

brooke@pcea.net

#### **EVENTS/TRADE SHOWS**

EXHIBIT SALES Frances Stewart 678-817-1286 | frances@pcea.net TECHNICAL CONFERENCE

Mike Buetow 617-327-4702 | mike@pcea.net

#### SUBSCRIPTIONS

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. To subscribe, visit pcdandf.com or circuitsassembly.com and click on Subscribe. For changes or cancellations to existing subscriptions: subscriptions@pcea.net

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by Printed Circuit Engineering Association, Inc., PO Box 807 Amesbury, MA 01913. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

© 2022, Printed Circuit Engineering Association, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/ CIRCUITS ASSEMBLY is forbidden without written permission.

#### THE ROUTE

MIKE BUETOW PRESIDENT

## Training Begets Retaining

OXCONN WAS IN the news (again) last month,

this time for alleging competitors are poaching its employees.

The complaints were levied specifically at rivals in Vietnam, where the world's largest ODM/EMS is expanding its factories as major customers like Apple shift production away from China, in part to avoid being a pawn in the geopolitical tug-of-war between the US and China.

Foxconn, which currently employs about 60,000 workers in Vietnam, asserts its EMS competitors are establishing their own operations near Foxconn's to make it easier to entice workers to jump ship.

Poaching complaints are hardly new, of course. Mexico is notorious for workers relocating *en masse* from company to company in pursuit of everything from higher pay to better food in the plant cafeteria.

Audrey McGuckin, who spent 10 years as chief talent officer for Jabil and now consults to Kimball Electronics, among others, points out the top stress point for CEOs is talent. And a McKinsey study found only 5% of CEOs feel their organizations' talent management has been very effective at improving company performance.

Covid-related issues have raised the profile of workers and increased their bargaining power, at least in the current term. And for their part, staffers at all levels are taking advantage of the situation.

The issue isn't whether employees can or should switch jobs. It's what steps companies can and should take to ensure valued workers *want* to stay put. In short, what can companies do to keep workers?

Having a culture that respects and promotes employees is often cited, of course. But how do you get there?

Don Charron, CEO of Kimball Electronics, says developing the EMS company's bench was a point of emphasis upon its spinoff from its parent company in 2014. In an interview on McGuckin's podcast, he said, "We literally were one deep in several really important positions, not just in the leadership level but in middle management as well. And I thought about our practices around talent, and it was a concern to other leaders on the team, but we really didn't know how to approach it."

Kimball, which has more than 6,400 employees today, realized it needed a combination of formality, rigor and science for its talent acquisition.

Charron says Kimball put a framework in place in order "to have a tougher conversation, a better conversation with people about their personal development, and it ended up with insights that were more actionable." It all started, he acknowledged, with him and his leadership team getting priorities in place, then getting the priorities down to the workforce.

This tracks with studies performed by Harvard Business School professor Robert Kaplan, who has shown that among publicly traded companies, those that best communicated their goals and objectives throughout the entire organization were more profitable over time than those that fell short. Kaplan arrived at his conclusions through interviews of upper and middle management and hourly personnel, where he studied whether the message as conceived and intended by the ranking officers was understood and internalized at the lower levels.

Oscar Gonzalez, vice president of operations, Mexico at Mack Technologies agrees. In an interview on the PCB Chat podcast this spring, Gonzalez said, "I think the best companies [in Mexico] are retaining talent. ... There's been studies on the key elements people look for. Competitive salary. Tasty food in the cafeteria. Being treated with dignity and respect. And training, the amount of hours you provide employees training."

In my experience, middle management is where communications break down. Often those promoted to lower-level management positions are thrust into the role due to an unanticipated need and based on their skills and performance in operations or sales. They are not trained for their new responsibilities, nor are they given time to acclimate to the role under the watch of a skilled mentor. They are handed a budget, a handful of direct reports, and basically told to make it work. Those who lack flexibility and acuity quickly find themselves in tricky situations, without the tools to resolve them appropriately.

Workers, for their part, have a once-in-a-generation opportunity where they don't need to hang around waiting and hoping for an internal change.

As Gonzalez says, training helps retain valued employees. The best printed circuit engineering training program of the year is PCB West, which takes place Oct. 4-7 at the Santa Clara (CA) Convention Center. Registration is open at pcbwest.com.

The greater economy is outside our control, but every company can study their internal goals and objectives, and put into place bidirectional communications systems that ensure those priorities are heard and met throughout the organization.  $\Box$

## Measure PCB Surface Finishes ENIG, EPIG, EPAG & ENEPIG

- XRF with Automated X-Y Table

- Increased Throughput

- Improved Reliability

- IPC 4552 B & IPC 4556

Measuring Made Easy®

www.fischer-technology.com | info@fischer-technology.com | 860.683.0781

#### **PCDF** People

Averatek appointed Michael V. Carano vice president of quality. Carano brings 40 years of electronics industry experience to Averatek, with expertise in manufacturing, chemicals, met-

als, semiconductors, medical devices and printing.

Fresh Consulting named **Rob Blomstrom** PCB design engineer.

SEMI named Joe Stockunas Americas president. Before joining SEMI, he served as executive vice president and corporate officer of Nordson, overseeing the company's worldwide electronics systems business.

#### **PCDF Briefs**

Altair in June acquired Concept Engineering for an undisclosed sum. Concept Engineering provides automatic schematic generation tools, electronic circuit and wire harness visualization platforms, and electronic design debug tools.

Atotech sold its 1,000th horizontal electrolytic copper plating line.

**Eltek** in June reported a fire in one of the production rooms in its plant in Petach-Tikva, Israel. The fire damaged part of the production line in that room and was extinguished without harming staff.

The European Union and Taiwan have set up a platform to work together on semiconductor supply chains.

Prototron Circuits added two PHI lamination presses.

The **SEMI Foundation** has been awarded \$1.5 million to design and develop the SEMI Career and Apprenticeship Network (SCAN) in Michigan.

**TPCA** is publishing a roadmap for PCB smart manufacturing in Taiwan. Chairman Maurice Lee, a senior consultant at **Unimicron**, says "member cohesion, industry competitiveness enhancement, and sustainable new value" and a high-value, low-carbon Taiwanese PCB industry are the main goals for his term.

Westak Circuits installed four Tagarno digital microscopes.

WUS Printed Circuit plans to spend \$280 million on a new production facility in Thailand.

## Technical Conference Program Set for PCB West 2022

**PEACHTREE CITY, GA** – The PCEA Conferences Task Group announced the technical program for PCB West 2022, featuring nearly 50 presentations and more than 110 hours of in-depth electronics engineering training.

Among the industry experts on tap for this year's show are Rick Hartley, Susy Webb, Thomas Chester and Dan Beeker. The conference will be held October 4 to 7 at the Santa Clara Convention Center and features classes for every level of experience, from novice to expert.

The scope of classes ranges from basics on design engineering and DfM, to designing and building advanced HDI and routing high I/O count chip packages, board stackup, circuit grounding, low layer-count (IoT) board design, high-frequency design, thermal management, and a complete virtual plant tour of a flexible circuit manufacturing facility. New courses this year include RF and microwave design, PCB layout of DDR memory, mechanical design, and raw material selection.

To drive engagement between experts and attendees, three panel discussions have been arranged on topics ranging from leading-edge component packaging drivers, emerging technologies, and discussions on careers in electronics engineering. These open forums are designed to spur lively interactive discussions on what electronics engineers can expect over the next 12 to 24 months.

"Printed circuit engineers are ready to get back to face-to-face events, and the PCB West technical conference has all the reasons they need to make their return to live interaction more than worth their time," said Mike Buetow, conference director, PCB West.

Registrants who sign up by Sept. 6 can take advantage of the Early Bird Special discounts for the conference, which features 49 presentations and panel discussions spanning 114 hours of classroom time.

For the first time, the program was developed by committee, as more than 70 abstracts were reviewed by the PCEA Conferences Task Group. The task group is made up of nine industry veterans with more than 270 years

of cumulative experience in the printed circuit industry. An exhibition featuring more than 100 leading

suppliers to the electronics design and manufacturing industry will be held October 5. For more information, visit pcbwest.com.

## PCB West Keynoter Dr. Brian Toleno to Focus on Where Electronics Meets Virtual Reality

**PEACHTREE CITY, GA** – The metaverses offer myriad opportunities not just for users but for developers of computing devices. As that market takes off, what novel innovations in materials and production will be needed for printed circuit designs to meet the requirements for weight, size, and functionality?

Those are the questions Dr. Brian Toleno, manager, Applied Materials at Meta's Reality Labs, will tackle when he keynotes this year's PCB West conference. His talk, Augmented and Virtual Reality, the Next Computer Revolution, will describe the current market, use cases, and the technology all around AR/VR, with a focus on the printed circuit board aspects.

At Meta, Dr. Toleno leads a multi-disciplinary team that works on the material challenges in Meta's consumer electronics hardware. These devices include VR headsets (Quest 2), smart glasses (Ray-Ban Stories), Portal smart screens and other exciting devices that help bring people together.

Dr. Toleno is a leading expert in materials science for electronics applications. Prior to Meta, Dr. Toleno was director of new technology at Microsoft, working on the

# Via Filling Solutions

## **Thermal Release**

Conductive/Non-Conductive Paste AE Series are long selling products for PCB/substrate thermal release. The pastes are filled into vias of PCBs/substrates by screen printing. Solvent free Tatsuta original formulation enables void less via filling with excellent long hour workability.

## **Reliable Connection**

TLPS conductive Paste MP series: "Metalizing Paste" is for highly reliable connection in PCBs/substrates. "Metallizing paste" contains solder and metal particles, which form inter metallic compounds(IMC) by thermal compression bonding. The IMC results more reliable connection.

## Via Filling&Circuitry Forming

Low temperature curable conductive paste SW Series forms circuitries on various PCBs/substrates. The pastes can be filled into vias simultaneously when forming circuitry, which shorten your process time and improve efficiency.

## Agent JFE Shoji Electronics Corporation Representative : Takeshi Mori

TEL: +81-3-5203-5643 EMAIL: takeshi-mori@jfe-shoji-ele.co.jp

#### **CA** People

Arch Systems appointed **Benjamin Freeman** vice president of engineering. Freeman specializes in analytics and technology-assisted optimization of physical processes.

Restronics Mid Atlantic named Matthew Osborne managing partner.

Sanmina promoted **Rodrigo Sierra Avila** to acting plant manager, Guadalajara.

Yamaha Motor Europe SMT Section appointed Kamil Stasiak product marketing manager.

Yamaha named Andy Wittbrodt key account manager. He joins Yamaha with 27 years of technical sales and service operations experience in electronics.

Zestron Americas appointed John Neiderman US and Canada sales manager. Neiderman has over 20 years of sales and technical experience in electronics manufacturing.

#### **CA Briefs**

Absolute EMS installed a VJ Electronix XQuik II Plus.

AIM Solder signed Cabiotec as distributor for its full line of products in Italy.

Alpha Circuit purchased and installed two Galaxy 30µ AOI machines.

**Cobham Mission Systems** purchased a photon steam aging system from **Hentec Industries/RPS Automation**.

Cogent Technology installed a YJ Link YLM laser marker.

**Compal** and **Pegatron** are reportedly expanding production in Vietnam, while Vietnam is poised to increase minimum wage amid rising inflation.

**DICA Electronics** deployed a **Pleora Technologies** visual inspection system.

**Flex** is building a new 145,000 sq. ft. facility in Jalisco, Mexico. The site will serve as an in-region automotive manufacturing hub.

GJD Manufacturing invested in a Hanwha Techwin SM482Plus SMT line.

**Incap Slovakia** added a selective soldering machine and a new SMT line to its Námestovo factory.

Hololens and director of global product management for underfills and encapsulants at Henkel. He was also a director of SMTA. He has a doctorate in chemistry from Penn State University and a bachelor's of science in chemistry from Ursinus College.

His talk takes place Oct. 5 from 11 a.m. to 12 p.m. at the Santa Clara (CA) Convention Center. There is no fee to attend Dr. Toleno's presentation, but advanced registration at pcbwest.com is required.

"Virtual reality is much further along than many people realize," said Mike Buetow, conference director, PCB West. "It has more daily transactions than the two largest digital currencies combined. Dr. Toleno has a deep knowledge of electronics manufacturing, and I can't think of a better person to explain the computing requirements from the cloud, the edge and localized devices this future will require."

## PCD&F's Annual Designers' Salary Survey Open

**PEACHTREE CITY, GA** – PRINTED CIRCUIT DESIGN & FAB is undertaking its annual salary survey of printed circuit board designers, design engineers and other layout specialists.

Results will be published in an upcoming issue of PCD&F. The data collected are revealed only in the aggregate, and no individual data will be revealed.

Designers for years have taken advantage of the results to benchmark their salaries, benefits and credentials against peers. The survey link is here: https://www.surveymonkey.com/r/N989JS3.

Because this is a survey, not a poll, the audience being surveyed is not selected or controlled.

## Vector Fabrication to Invest \$60M in Vietnam PCB Plant

**DA NANG, VIETNAM** – Vector Fabrication has received an investment license for a PCB and MEMS factory, with plans to invest \$60 million, according to reports.

The factory is expected to be 40,000 sq. m., and the first phase is expected to begin in the first quarter of 2025. The plant plans to begin manufacturing MEMS as of the first quarter of 2027.

The fabricator will build two-, four-layer and multilayer PCBs, probe cards and IC burn-in boards.

Vector reportedly develops substrates for Intel.

## Ampel Acquires US Circuit, RMC

**ELK GROVE VILLAGE, IL** – Ampel has acquired fellow fabricators Rocky Mountain Circuits and US Circuit for an undisclosed sum.

Production at Boulder, CO-based Rocky Mountain Circuits is shutting down, and existing orders will be moved to Ampel and US Circuit.

RMC will maintain a sales and engineering support office, however.

Ampel was founded in 1983 and also owns Lazer-Tech, Image Circuits, Tritech PCB, PC Specialties, Crimp Circuits and Texas Circuitry.

## Nitto Acquires Bend Labs

FARMINGTON, UT - Nitto Denko acquired Bend Labs for an undisclosed sum.

The sensor device technology company merged into Nitto, starting business as Nitto Bend Technologies.

Bend's flexible sensor measures bend, stretch and force. The flexible sensor is expected to meet automation demands in the automotive field and remote monitoring

## Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

**BluePrint**·PCB

**CAM350**

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

- Use DFM analysis to analyze a flex or rigid-flex design for potential fabrication or bend related defects

Use Stack Up Visualizer and Blueprint's Rigid-Flex Stackup template to easily manage and document rigid-flex stackups.

A rigid-flex design in 3D. Shown with layers spread to improve visualization of the layer stackup. Use Rigid-Flex and Inter-layer DFM analysis to analyze flex and rigid-flex designs.

For more information visit downstreamtech.com or call (508) 970-0670

**Infestos Sustainable Solutions** said it would initiate buyout proceedings for all outstanding ordinary shares of **Neways Electronics.** Infestos currently owns more than 95% of the company's shares.

**iNEMI** was awarded \$290,865 from the **National Institute of Standards and Tech-nology's** Advanced Manufacturing Technology Roadmap Program to develop a 5G/6G roadmap.

IPC established a subsidiary in Munich.

Jabil announced a manufacturing collaboration with Cardo Systems, a maker of wireless group communications and entertainment systems for motorcycle riders.

**Jaltek** opened a new EMS facility near Luton, UK, that increases its manufacturing space by 50%.

Omega EMS is producing Eguana Technologies products in San Jose.

**PDR Rework Systems** hired **Restronics** as manufacturers' representative in Southern California.

**Pektron** purchased 15 **Yamaha** YRM20 placement machines.

**Pro-Active Engineering** integrated an **ASM** DEK NeoHorizon screen printer and three SiplaceTX placement platforms at its EMS plant.

**PVA** received a patent in Japan for an optical bonding machine with cure in place and visual feedback.

A Sky One France subsidiary has acquired EMS provider Malaga Aerospace Defense & Electronics Systems SAU (MADES) from American Industrial Acquisition Corp. (AIAC). Terms were not disclosed.

SMarTsol Technologies added Austin American Technology to its line card in Mexico.

**Stewart Technology** added two **Nordson** Cerno 300.1S selective soldering systems to its production facility in Tweedbank, Scotland.

Spain's government has approved a plan to spend €12.25 billion on the semiconductor and microchip industry by 2027, Economy Minister Nadia Calvino said, including €9.3 billion to fund the building of plants.

ViTrox Technologies named Ostec-SMT sales channel partner in the Russia region.

VJ Electronix appointed Southwest Systems Technology to represent its component counting systems in Texas, Oklahoma, Arkansas and Louisiana.

Yekani closed its manufacturing facility in South Africa and auctioned off the assets.

in the digital healthcare field. Nitto anticipates this technology to be used in sports and robotics as well.

The impact of this acquisition on Nitto's consolidated earnings forecast for 2022 is insignificant.

Nitto develops new products and services in three domains: information interface, next-generation mobility and human life.

## PCB Technologies Launches SiP Subsidiary iNPACK

**OCEAN TOWNSHIP, NJ** – PCB Technologies is launching a subsidiary to provide systemin-package solutions. Beginning this month, iNPACK will focus on high-end technology that contributes to improved signal integrity and reduces unwanted inductance effects.

iNPACK will provide SiP, semiconductor packaging, organic substrates (25µm lines and 25µm spacing), and 3-D, 2.5-D and 2-D packaging solutions for aerospace, defense, medical, consumer electronics, automotive, energy and communications industries.

"The new company incorporates innovative interconnects as part of its substrates and micro-assembly process capabilities," said Jeff De Serrano, PCB Technologies' president for North America. "Our technological solutions can more than double the electronic functionality in the same form factor and create substrate-like PCBs. To top it off, our lead times are only six months long. The goal is to support our customers from design concept to production, all under the same roof, while utilizing unified design rules."

## GPV, Enics to Merge, Creating Europe's 2d Largest EMS

**VEJLE, DENMARK** – Europe's EMS industry was shaken up in June as GPV and Enics announced a pending merger to form the continent's second-largest EMS company with more than 7,500 employees and annual revenue of more than DKK 7 billion (\$990 million).

The transaction values the combined business at more than DKK 4 billion (\$566 million). Closing is subject to customary approvals, including from antitrust officials.

Danish industrial conglomerate Schouw & Co., listed on Nasdaq Copenhagen, will hold 80% of the merged entity, while the current owner of Enics, Ahlström Capital will hold 20%. Additionally, as a result of the transaction, Ahlström Capital will receive approximately EUR 60 million (\$63.1 million) in cash. The merger will create an international electronics group with more than 7,500 employees .

"This is a combination of two equally strong and very competent companies," said Bo Lybæk, CEO, GPV. "With the merger, we take yet another significant step on our growth journey. In 2018, we successfully acquired the Swiss electronics manufacturer CCS, which had revenue of DKK 1.6 billion. That lifted GPV into the top 10 of EMS companies in Europe, and we have since delivered solid results. Based on our trackrecord from the integration of CCS, we're now looking to repeat the success. Together with Enics, we're creating the second-largest EMS group headquartered in Europe."

Lybæk will lead the integration of the two businesses into the new combined company.

"Schouw & Co. and Ahlstrom Capital share similar values and both companies' legacy and long-term strategic outlook provided an excellent climate for negotiation," said Jens Bjerg Sørensen, chairman, GPV. Sørensen will become chairman of the merged company.

"At Schouw & Co., we have a clear strategy of making long-term investments in market-leading companies. With the merger between GPV and Enics, we will now create a leading player that can measure up to even the largest EMS companies, and which within a foreseeable number of years can reach DKK 10 billion in revenue," Sørensen added.

Following the deal, the merged entity will be Europe's second largest EMS com-

pany, behind Zollner.

Enics is among the industrial leaders in design, lean manufacturing, and development of test systems for some of the world's largest customers, while GPV is a full-service EMS provider specializing in managing high-mix product portfolios, application design and engineering for a strong range of market-leading customers.

"Enics and GPV are a perfect match. I look forward to laying the foundation for this strong European industrial platform. Together, both companies have even stronger capabilities to provide turnkey offerings that will make the combined company a success in the fast-changing EMS market. I'm confident that together we will be driving the sustainable success of our customers and leading the way to change how EMS companies operate in complex ecosystems," said Elke Eckstein, CEO, Enics.

Enics has seven factories in Europe and Asia across Finland, Sweden, Estonia, Slovakia, China, and Malaysia, while GPV has 12 factories located in Denmark, Switzerland, Germany, Austria, Slovakia, Mexico, Sri Lanka, and Thailand. Enics is focused on electronics manufacturing and test, while GPV also specializes in product application design, in-house mechanics, and cable-harness assemblies. GPV has been particularly successful with its box-build mechatronics products, an area where both Eckstein and Lybæk see great potential going forward, including for Enics' current customers.

Most of Enics' and GPV's customers are in the industrial segment.

## Align Capital Partners Acquires StenTech

MARKHAM, CANADA – Align Capital Partners has acquired StenTech for an undisclosed sum.

StenTech provides surface mount technology stencils, pallets, tooling and related components.

The company boasts more than 2,000 customers across North America.

## Proposed IPC Standard for Green Cleaners Open for Public Review

**BANNOCKBURN, IL** – A draft version of IPC-1402, Standard for Green Cleaners Used in Electronics Manufacturing, is now open for public review. The draft standard has been progressing through the standards process since fall of 2021 and, despite some minor delays in the draft development timelines – as is common during consensus-based standards development processes – the draft is now ready for public review through Jul. 15.

The draft IPC-1402 standard has been developed by volunteers and key governmental agencies from Asia, Europe and North America. This first-of-its-kind standard for the electronics manufacturing industry defines and sets minimum criteria for green cleaners – chemical cleaners meeting a defensible set of green chemistry requirements – used in electronics manufacturing processes. Also, this standard provides a core set of foundational environmental, health and safety requirements that aim to reduce impacts and improve the safety of cleaning products.

IPC encourages personnel whose company uses chemical cleaners on electronic products or components, or on machines and tooling used during operations and maintenance, to review the draft standard and provide comments to the authoring task group.

The draft document is freely available, and reviewers can participate in the process by submitting comments about this draft industry standard by mid-July. Reviewers can request a copy of the draft document and instructions on how to submit comments by emailing answers@ipc.org.

At the end of the public review period, comments will be consolidated, and the standards development team will work toward resolution of comments. Then, the final document will move to the ballot group for consensus vote. IPC-1402 is expected to be released in mid-December.

## PG Technoplast to Invest \$41M in Maharashtra, India

**UTTAR PRADESH, INDIA** – PG Technoplast signed a memorandum of understanding with the government of Maharashtra to invest Rs 3.15 billion (US\$41 million) in the state, according to reports.

The electronics manufacturing services provider has eight production sites in India. The company will work with Maharashtra Industrial Development Corp. to create the region's largest room AC manufacturing capacity.

"We are grateful to the government of Maharashtra for facilitating PG's push to provide its customers turnkey solutions for all home appliances," said Vikas Gupta, MD-Operations, PG Group. "The move will help bring room AC manufacturing to the Western region of the country, which historically has been concentrated in the Northern, and now Southern, parts of the country."

In the fiscal third quarter, the firm's net profit declined 2.6% to Rs 63.3 million, and sales increased 45% to Rs 2.7 billion compared to the same period last year.

## GPV to Construct Mechanics Factory in Thailand

**PHRAEKSA, THAILAND** – GPV Mechanics is constructing a 12,000m<sup>2</sup> mechanics manufacturing factory in Thailand. The facility will be built with room to grow, say reports.

"We are very much looking forward to serving our customers from the new factory in 2023. The main piling ceremony is an important first step in going forward with the construction work. Safety of our employees is key, and so is the safety of all involved in the construction of our new production facility. Our ambition is to execute the building construction with zero LTIs," said Bjørn Fiskers, managing director.

GPV currently has 7,100m<sup>2</sup> mechanics production and 15,000m<sup>2</sup> electronics production in Bangkok.

The company is also building a new 11,300m<sup>2</sup> electronics manufacturing facility in Sri Lanka.

# Is Your Current PCB Supplier Pushing Out Lead Times That Are Unthinkable?

## PCT Values Being A Partner, Not Just A Supplier

Operational Support to Assure Availability & Required QTA Lead Times

- Engineering Expertise to Advise on New & Emerging Technologies

- Customer Service "That Is Best In Class"

APCT PICASC

## The Solution Is APCT

## Work With A Partner, Work With APCT

APCT.com

408.727.6442

714.921.0860

APCT Santa Clara HQ 🗄 APCT Anaheim 🗄 APCT Orange County 🗄 APCT Wallingford 🗄 APCT Global 714.993.0270

203.269.3311 203.284.1215

## **APCT CAPABILITIES**

## **TECHNOLOGIES**

LEAD

0

QUAN

CERT

| RIGID                                                          |                                 |

|----------------------------------------------------------------|---------------------------------|

| Standard:                                                      | 2 – 28 Layers                   |

| Advanced:                                                      | 30 – 38 Layers                  |

| Development (NPI only):                                        | 40+ Layers                      |

| HDI; BLIND/BURIED/STACKED VIA                                  |                                 |

| Lam Cycles:                                                    | Up to 8x                        |

| Micro BGA Pitch:                                               | .2 Millimeters                  |

| FLEX / RIGID-FLEX                                              |                                 |

| Standard Flex:                                                 | 1 – 6 Layers                    |

| Rigid Flex:                                                    | 4 – 22 Layers                   |

| Rigid Flex HDI Lam Cycles:                                     | Up to 2x                        |

| D TIMES                                                        |                                 |

| RIGID                                                          |                                 |

| Standard:                                                      | 20 Days                         |

| 2 – 10 Layers:                                                 | 24 Hours                        |

| 12 - 24 Layers:                                                | 48 Hours                        |

| HDI; BLIND/BURIED/STACKED VIA                                  | 70 11 2                         |

| Via in Pad:<br>HDI :                                           | 72 Hours<br>5 – 15 Days*        |

|                                                                | nding upon # of Lam Cycles      |

|                                                                | haing oport in or carrie cycles |

| FLEX / RIGID-FLEX<br>Flex 1 – 6 Layers:                        | 5 – 15 Days                     |

| Rigid Flex 4 – 22 Layers:                                      | 7 – 15 Days                     |

| Rigid Flex HDI 2x Lam Cycles                                   | 20+ Days                        |

| NTITIES                                                        |                                 |

| Prototypes     Mid-Production                                  | on l                            |

| <ul> <li>Production Orders - with offshore solution</li> </ul> |                                 |

| TIFICATIONS                                                    |                                 |

|                                                                |                                 |

|                                                                | egistered at all sites          |

| AS9100D Certified     IPC 60     MIL-PRE-31032 Certified       | 12 Class 3 & 3A                 |

- MIL-PRF-31032 Certified (MIL-P-55110 Certified)

- MIL-P-50884 Certified

- IPC-6013

- IPC-1791 Trusted Electronics Qualified Manufacturers Listing (QML)\*

\*APCT Anaheim & Orange County Only

## Printed Circuit Board Solutions APCT Santa Clara HQ # APCT Anaheim # APCT Orange County # APCT Wallingford # APCT Global

APCT.com

APCT Santa Clara HQ 408.727.6442

714.921.0860

714.993.0270

203

203.269.3311 2

203.284.1215

## Report: 70% + of Electronics Supply Chain Lead Times to Increase into 2023

**PASADENA, CA** – Through the first quarter of 2023, more than 70% of lead times are forecast to increase, according to Supplyframe. During that time frame, analog, complex semiconductor (ASICs, MCUs, MPUs, PLDs), flash memory, non-ceramic capacitor, resistor and standard logic devices are forecast to rise in price with very limited exceptions. Most of the same devices will also remain at or exceed already elevated lead times.

From analog power to standard logic to ASICs and sensors, the active components market will be swimming in a sea of red indicators for the next four quarters. This is happening as strong demand continues; production is at capacity; there are extended lead times; and rising prices plague most devices.

Passive components are not as constrained as active ones. However, like active components, passive commodities also suffer from raw material challenges and labor shortages.

| PERIPHERAL PLUMMET                                                                                                                                                                   |      |               |       |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|------|

| Trends in the US electronics<br>equipment market (shipments only)                                                                                                                    | FEB. | % CH/<br>Mar. |       | YTD% |

| Computers and electronics products                                                                                                                                                   | 1.3  | -0.3          | 0.5   | 4.6  |

| Computers                                                                                                                                                                            | 4.2  | -2.9          | 1.5   | -2.0 |

| Storage devices                                                                                                                                                                      | 1.8  | -0.7          | 5.2   | 11.0 |

| Other peripheral equipment                                                                                                                                                           | 6.3  | 7.2           | -10.8 | 3.0  |

| Nondefense communications equipment                                                                                                                                                  | 1.3  | -3.1          | 1.1   | 9.2  |

| Defense communications equipment                                                                                                                                                     | -1.9 | -3.3          | 5.9   | 9.3  |

| A/V equipment                                                                                                                                                                        | 0.0  | 5.0           | 0.9   | 46.5 |

| Components <sup>1</sup>                                                                                                                                                              | 2.2  | -0.1          | 0.1   | 13.8 |

| Nondefense search and navigation equipment                                                                                                                                           | 0.4  | -1.8          | 2.5   | 1.2  |

| Defense search and navigation equipment                                                                                                                                              | 1.5  | -1.7          | 0.4   | 0.2  |

| Medical, measurement and control<br>'Revised. *Preliminary. <sup>1</sup> Includes semiconductors. Seasonally adjus<br>Source: U.S. Department of Commerce Census Bureau, June 2, 202 |      | 0.3           | 1.4   | 1.3  |

| US MANUFACTURING INDICES                              |      |      |      |      |      |

|-------------------------------------------------------|------|------|------|------|------|

|                                                       | JAN. | FEB. | MAR. | APR. | MAY  |

| PMI                                                   | 57.6 | 58.6 | 57.1 | 55.4 | 56.1 |

| New orders                                            | 57.9 | 61.7 | 53.8 | 53.5 | 55.1 |

| Production                                            | 57.8 | 58.5 | 54.5 | 53.6 | 54.2 |

| Inventories                                           | 53.2 | 53.6 | 55.5 | 51.6 | 55.9 |

| Customer inventories                                  | 33.0 | 31.8 | 34.1 | 37.1 | 32.7 |

| Backlogs                                              | 56.4 | 65.0 | 60.0 | 56.0 | 58.7 |

| Source: Institute for Supply Management, June 1, 2022 |      |      |      |      |      |

## Hot Takes

- Global semiconductor equipment billings grew 5% yearover-year to \$24.7 billion in the first quarter. Sequential billings in the seasonally soft first quarter declined 10%. (SEMI)

- Total semiconductor sales in 2022 are forecast to increase 11%, the same growth rate that was forecast in January. (IC Insights)

- Tech manufacturing plants are operating at 87% capacity, and that's expected to increase 5.8% throughout 2022. Capital expenditures are forecast to grow 7.2% during the same period. (Institute for Supply Management)

- The worldwide infrastructure as a service (IaaS) market grew 41% in 2021 to total \$90.9 billion, up from \$64.3 billion in 2020. Amazon retained the No. 1 position in the IaaS market in 2021, followed by Microsoft, Alibaba, Google and Huawei. (Gartner)

- Despite chip demand showing signs of a downturn since the start of 2022, the capacity expansion spree at foundry houses seems unstoppable, sparking concerns that overcapacity may hit the global foundry market in 2024. (DigiTimes)

- Samsung remained the world's largest DRAM supplier in 2021, with sales of nearly \$41.9 billion and 44% market share. (IC Insights)

- Seventy-eight percent of CFOs plan to maintain or increase enterprise-wide digital investments in the next two years. (Gartner)

- The augmented reality market was worth \$9 billion in 2021 and is estimated to grow to \$150 billion by 2030. (Research and Markets)

- Sixty-three percent of executives plan to make **compensa***tion adjustments* in response to high inflation. (Gartner)

- Smartphone production fell 13% sequentially in the March quarter to 310 million units. (TrendForce)

- Smartphone shipments will decline 3.5% to 1.31 billion units in 2022. (IDC)

- The automotive testing inspection and certification market was valued at \$22.9 billion in 2020 and is expected to grow at a CAGR of 4.7% over the forecast period to reach \$31.6 billion by 2027. (Research and Markets)

| KEY COMPONENTS                                                                                                                                                            |       |       |       |                          |                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------------------------|---------------------------|

|                                                                                                                                                                           | DEC.  | JAN.  | FEB.  | MAR.                     | APR.                      |

| EMS (North America) <sup>1</sup>                                                                                                                                          | 1.55  | 1.58  | 1.52  | 1.44                     | 1.36                      |

| Semiconductors <sup>2</sup>                                                                                                                                               | 28.3% | 26.8% | 26.2% | <b>23</b> % <sup>r</sup> | <b>21.1%</b> <sup>p</sup> |

| PCBs <sup>3</sup> (North America)                                                                                                                                         | 1.17  | 1.18  | 1.16  | 1.05                     | 1.03                      |

| Computers/electronic products <sup>4</sup>                                                                                                                                | 5.32  | 6.46  | 6.38  | 6.45 <sup>r</sup>        | 6.39 <sup>p</sup>         |

| Sources: <sup>1</sup> IPC, <sup>2</sup> SIA (3-month moving average growth), <sup>3</sup> IPC, <sup>4</sup> Census Bureau, <sup>p</sup> preliminary, <sup>r</sup> revised |       |       |       |                          |                           |

# CAN'T FIND The right material?

We offer one-of-a-kind adhesive and encapsulation solutions

CREATE MY CUSTOM FORMULATION

## Innovative Technology: Enabling or Disruptive?

Fabricators and designers must communicate about new technology to verify its viability.

MORE OFTEN THAN not over the past couple of decades, new technologies, processes and options we fabricators have been asked, begged or threatened to add to our repertoire of offerings were ones that could be best considered disruptive. What's disruptive to a manufacturer may seem benign to the casual eye, as often the technology – or process – that is most disruptive is a simple one.

Indeed, sometimes that technology is nothing more than the rebirth of an older, tried-and-true, albeit significantly tweaked, process. REACH, and the prior RoHS, caused much disruption, and yet most of the plating chemistries and surface finishes in use today are essentially highly refined formulas of older plating technologies such as ENIG, silver and tin.

Old or new, disruptive technologies tend to be challenges for several reasons. First is understanding the technology and how to process it so it works as intended. Second is determining what equipment is needed to cost-effectively and robustly apply the new technology. Finally, finding enough customers to consistently order product that uses the technology, so everyone remembers what it is and how to process it!

Truly new paradigm-shifting technologies hit the scene as "must haves" so a product can function. While disruptive to manufacturers, in some ways the more off-the-wall a technology seems, the easier it is to decide whether to embrace it or wait to see if it sinks under the weight of its own hype. These disruptive technologies more typically challenge everyone to understand not only how to apply them, but how to measure success or failure so yields and costs can be determined.

In all cases, what makes disruptive technologies so unruly boils down to two issues: First is the learning curve and capital investment needed to provide the technology, and second is gaining consensus among customers that the technology is a better alternative to more traditional technologies, and they will purchase enough to warrant the human and capital investment. Probably most frustrating for fabricators is when a buyer provides no apparent reason other than "because" for specifying a new technology. The fabricator's goal is to supply quality product they understand and can safely and consistently produce, not (inadvertently) become a customer's R&D center, with the concurrent risks and costs.

Every new technology has at least two sides. At a recent industry gathering, a supplier mentioned a current disruptive technology we had difficulty working our way through was only one of a slew of new "enabling" technologies available to the industry. Enabling? Not to me. That is when the communication gap between design application and manufacturing competence became evident. As this conversation continued, I heard a different spin as to why a particular new technology was being specified. Understanding the benefits from the end-product perspective began to make sense and explained why this customer would have specified it, as well as why its use may become widespread in the future. The tutorial was strictly from a value-add design perspective, and it was compelling. When asked if the design community knew of the fabrication challenges the new technology caused that impacted yield and lead times, in addition to cost, the answer was honest: "Probably not."

What's enabling to one party can be disruptive to another. Fabricators often do not understand the nuances of pushing design to meet challenging performance objectives but do fully understand robust, time-proven manufacturing techniques. Equally, when a designer chooses to move toward a new technology, they may be excited by the functionality it offers but most likely is unaware manufacturing the board could lead to lower yield, longer lead times and ultimately higher costs.

The real issue is understanding the risks involved with embracing – or ignoring – new technology. The risks include, "Will it work, or will it only work if executed flawlessly? Will the new technology pass the test of time? Most important, will widespread use of the technology lead to cost-effective processes or equipment to ensure consistency from one application to another and from one supplier to another?"

As a fabricator, it is more important now than ever to be in touch with customers' designers to understand what they are attempting to accomplish. Equally for designers, it is essential they are in contact with all their PCB suppliers, especially the behind-the-scenes process gurus, so everyone understands the manufacturability of new technology in the real world of the shop floor.

This gets back to the need for suppliers knowing their customer and customers knowing their suppliers – and not just at the buyer/sales rep level but at the designer/manufacturing engineer level. Knowing the intended end-result a new technology enables, as well as how disruptive that technology may be when

continued on pg. 49

PETER BIGELOW is president and CEO of IMI Inc.; pbigelow@imipcb. com. His column appears monthly.

## All Wet: PCB Packaging, Shipping and Storage

Limiting PCB moisture absorption is the full responsibility of the supplier. How to pack boards right.

PCB SUPPLIERS WHO use good packaging methods are keeping their products safe from physical damage incurred during transit from the manufacturing facility to customers' warehouses. Equally important, these packaging practices help ensure shelf-life expectancy by preventing moisture absorption.

To protect their orders, PCB buyers should require suppliers strictly follow corporate shipping specifications. Nothing is more frustrating than waiting for quality product to be built, only to have it damaged because of poor packaging practices. It's just as frustrating when boards become useless while sitting on the shelf.

PCBs can be very heavy. Their sharp corners sometimes wreak havoc on the corrugated cardboard boxes in which they are shipped. A good freight spec should state boards are to be vacuum-packed with a bubble wrap base, with no more than 25 boards to a stack. When a board is oversized or heavier than normal, 10 to 15 pieces is the best option. Whatever number is used, the packaging should be consistent in count for a particular shipment.

Extra care should be taken for flexible or very thin, rigid PCBs less than 0.028" thick. They should be packaged with stiffening material on the top and bottom of the bundle to help prevent warping.

A humidity indication card (HIC) and desiccant are to be placed within the package as well. The HIC should be placed inside on top of the PCBs for easy review. The desiccant should be placed along the side or edge of the bundle, so it doesn't contribute to bending or warping caused by the stress of the vacuum packaging.

Each PCB bundle should have a sticker affixed detailing the part number, date code and number of pieces per bundle. More than one date code of the same product may be shipped together if they are segregated and marked as such.

X'd-out panels, if allowed by your PCB fabrication specifications, should be packaged separately and clearly marked.

The individual packages of PCBs should be placed tightly in a box, with Styrofoam or other shockabsorbing material placed between the packages and the wall of the shipping container. The PCB corners should be protected, as they can be easily dinged or dented while in transit.

The weight of each box should not exceed 30 lb. Boxes may have exterior strapping applied when the PCBs are oversized or heavier than normal.

Each box should have a sticker on either end iden-

tifying its contents, including the part number, purchase order number, date code and number of pieces within the box.

Each part number shipped should come with a packing slip and "proof of quality" documentation, including (but not be limited to):

- The certificate of compliance

- A first article or dimensional report

- A microsection report to include a solderability test with a cross-section

- An electrical test report

- An ionic contamination report

- A TDR report (controlled impedance, when applicable)

- Any material certifications

- Any other documentation required by the purchase order.

When the product is shipped, the supplier should notify the customer's purchasing, receiving and accounting departments of shipment method and tracking number. The commercial invoice and electronic copies of the quality paperwork should be included in case such documentation for the shipment is lost in transit.

As crucial as proper PCB packaging is, the storage of the boards once they reach the customer is just as vital. Other than opening one of the packages to verify the PCBs meet the criteria of the print and the documentation received, the best bet is to leave the boards in their original packaging.

A bare board begins to absorb moisture immediately upon leaving the factory. The amount of moisture absorbed depends on a variety of factors, including:

- Base material used in manufacturingManufacturing environment

- Decleasing method

- Packaging method

- Shipping temperatures (from the cold bellies of aircraft or the humid transit of a sea shipment to hot delivery trucks)

- Customer storage and inventory procedures.

Vacuum sealing and the use of desiccant only delay

or lessen moisture absorption. They do not prevent it. The longer a PCB is stored on a shelf, the greater

the chance it will absorb moisture, which can manifest in the assembly operation as delamination. Delamination is caused either by moisture or manufacturing defects. If a problem PCB is determined to be structur(boardbuying.com); greg@directpcb.com.

GREG

PAPANDREW

has more than 25

years' experience selling PCBs

directly for various

leading distributor.

He is cofounder of

Better Board Buying

fabricators and

as founder of a

continued on pg. 49

## **Printed Circuit Engineering Professional**

The comprehensive curriculum specifically for the layout of printed circuit boards

The **Printed Circuit Engineering Professional** curriculum teaches a knowledge base and develops a competency for the profession of printed circuit engineering layout, based on current technology trends. It also provides ongoing reference material for continued development in the profession. The 40-hour course was developed by leading experts in printed circuit design with a combined 250 years of industry experience and covers approximately 67 major topics under the following headings: Basics of the profession, materials, manufacturing methods and processes; circuit definition and capture; board layout data and placement; circuit routing and interconnection; signal-integrity and EMI applications; flex PCBs; documentation and manufacturing preparation; and advanced electronics (energy movement in circuits, transmission lines, etc.). Class flow: Books sent to students prior to an instructor lead review. This is followed by an optional exam with a lifetime certification that is recognized by the PCEA Trade Association.

The course references general CAD tool practices and is vendor-agnostic. Instructors include Mike Creeden, CID+, who has over 44 years of industry experience as an educator, PCB designer, applications engineer and business owner; and Tomas Chester, P.Eng., CPCD, who has designed over 100 circuit boards through all phases of the product lifecycle, and managed a variety of multifaceted, interdisciplinary projects, from simple interconnect designs to complex microprocessors. For Information or Registration: https://pcea.net/pce-edu-design-engineer-curriculum/

Upcoming Class Openings: More added each month! July 11-15

## AUTHORS

Mike Creeden

Gary Ferrari

Susy Webb

**Rick Hartley**

Steph Chavez

## Printed Circuit Engineering Professional

Table of Contents:

#### Chapter 1: Professional Overview

- 1.1 Printed Circuit Engineering Layout Overview Profession overview

- **1.2 Basic Fabrication of a Printed Circuit Board** Materials and construction

- 1.3 Basic Assembly of a Printed Circuit Board Materials and process

- **1.4 Basic Electronics in a PCB** Fundamental understanding and concepts

- 1.5 Basic Printed Circuit Engineering Layout Overview – Layout process

- **1.6 Project Management (PM)** Enabling project success and accountability

- 1.7 Communication throughout the process

#### Chapter 2: Circuit Definition & Capture

- 2.1 Libraries to Bill of Material (BOM) Integrated library: symbols, land patterns

- **2.2 Surface Mount and Thru-Hole Technology** Components and process

- 2.3 Schematic Types and Conventions– Functional, logic, flat and hierarchal

- 2.4 Schematic Symbol Placement Orderly circuits improve comprehension

- 2.5 Schematic Review Complete and accurate

- 2.6 Circuit Board Types Rigid, Flex and Printed Electronics

- 2.7 IPC MIL Standards and Specifications Reference listing of standards

- 2.8 Verification, Testing, Compliance & Qual. Assurance

- 2.9 Mechanical Board Information –Physical requirements

- 2.10 Database Links and Iterative Data Exchange Development iterations

#### Chapter 3: Board Layout Data & Placement

- 3.1 Board Parameters Set-up CAD environment

- 3.2 Stackup Design Z-Axis relationship

- 3.3 Constraints and Rules Define and implement accurate reliability

- 3.4 Placement for Assembly Performance and buildability

- **3.5 Placement of Components** Solvability, performance, and manufacturing

- 3.6 Schematic Driven Placement Cross-probing

- 3.7 Placement Dense Digital Circuits (LSI) Large Scale Integration

- **3.8 Placement Power Delivery** Source, distribution, and usage

- 3.9 Placement Mixed Circuit (RF/HSD) Together

- 3.10 Placement Review Milestone Approval for routing

## Chapter 4: Circuit Routing & Interconnection

- 4.1 General Overview of Routing Fundamental parameters

- 4.2 Routing Dense Digital Circuits Modular approach

- 4.3 Routing with Signal Integrity Applications Managing energy fields

- **4.4 Routing Power Delivery** Source, Distribution, and Usage

- **4.5 Routing RF Circuits** Managing dissipation and loss

- 4.6 Routing Review Milestone Approval of routing

## Chapter 5: Flex Printed Circuits (FPC)

- 5.1 Flex and Rigid-Flex Technology Overview and Introductions to FPC

- 5.2 Flexible Printed Circuit Types IPC definition

- 5.3 Flexible Circuits Applications Industry sectors and usage

- 5.4 Materials for Flexible Circuits Properties and process

- 5.5 Design Start Considerations Physical and electrical

- 5.6 FPC Stackup Constructions Usage and process

- 5.7 Flex Design Practices Physical and electrical aspects

- **5.8 Production Process Consideration** Process flow

- **5.9 Conductive Surface Finishes** Overview of types and process

- 5.10 Stiffeners Types and applications

- 5.11 Shielding Material EMI and EMC considerations

- 5.12 Design for Manufacturability and Assembly Unique concerns building FPC

#### Chapter 6: Documentation & Manufacturing Preparation

- 6.1 Documentation Overview Prepare for the final design effort

- 6.2 Resequencing Reference Designators Backannotation

- 6.3 Silkscreen Providing visual intelligence

- 6.4 Industry Standards Design, document and build compliance

- 6.5 Post-processing Procedure Know what to expect at your company

- 6.6 Manufacturing Deliverables Documentation

- 6.7 Fabrication Drawing Instructions to fabricate the bare board

- 6.8 Assembly Drawing Reference drawing used to assemble the PCA

- 6.9 Schematic Database and Drawing Circuit capture and BOM origin

- 6.10 Bill of Materials (BOM) Controlling document

- 6.11 Final Deliverables Formats and creation process

- 6.12 Transfer to Manufacturer Manufacturing interface

#### Chapter 7: Advanced Electronics, EM Applications

- (During the review class only cursory coverage of Chapter 7 will be provided due to the advanced nature of this content.)

- 7.1 Energy Movement in Circuits –EM Theory

- 7.2 Critical Frequencies in Circuits on PC Boards Frequency and Rise Time (Tr)

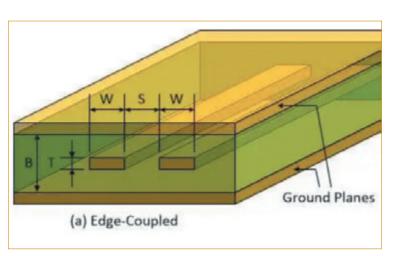

- **7.3 Transmission Lines in PC Boards** Relational nature in electronics

- 7.4 Understanding Impedance of Transmission Lines Modification from layout

- 7.5 Impedance Control of Transmission Lines Controlling impedance in layout

- **7.6 Controlling Impedance of Digital ICs** Controlled and set to specific values

- 7.7 Controlling Noise Margin Critical lengths understanding

- 7.8 Crosstalk and Cross-coupling Capacitive and inductive coupling

- 7.9 Controlling Timing of High-speed Lines Timing matched, not length

## ECTC Highlights Next-Generation Packaging Challenges

Large crowds mulled the latest substrate trends and new developments in 3-D IC hybrid bonding.

The IEEE Electronics Components and Technology Conference (ECTC) returned to an in-person conference at the end of May with more than 1,500 attendees, domestic and international. Attendance in San Diego matched pre-pandemic numbers. While some presentations remained virtual, using video recording, many were onsite. A variety of electronics packaging topics were discussed. Judging by the crowded rooms, this year's hot topic was 3-D IC hybrid bonding.

Advanced packaging. A pre-conference Heterogeneous Integration Roadmap workshop discussed trends in networking for the future and new developments in advanced packaging for high-performance computing and data centers. The workshop concluded with a panel of presenters discussing the latest trends in medical health and wearables.

Plenary sessions covered some of the latest topics. The MicroLED display session focused on highvolume manufacturing progress and challenges. In a session on the evolution of IC substrate technology, panelists from Intel, Amkor, Ajinomoto, AT&S and Atotech discussed the latest substrate trends.

The special session – Meeting Next Generation Packaging Challenges from Chiplets to Co-packaged Optics – included panelists from AMD, Cisco, Marvell and Synopsys (FIGURE 1). Panelists discussed the importance of co-design and changing the approach to design, including system-level design. The combination of digital and photonics is coming. Integrating this in 3-D will include the laser, modulator, filters and detectors. Interfaces and the design platform are important for robust manufacturing, including product quality, debug and traceability, and in-field optimization. The panel concluded that, with increased use of chiplets, continued work is required in the areas of test and known good die (KGD), thermals, power deliver and system-level integrity. Adoption of standards such as the recently introduced UCIe is important to align the industry around an open platform to enable chiplet-based solutions. Thermal management remains one of the major bottlenecks with 3-D.

A special night session focused on the US Department of Defense (DoD) in the state-of-the-art heterogeneous integration (SHIP) program. The opening statement from the office of the Undersecretary of Defense for Research and Engineering explained the backdrop of the program. Speakers from Intel and Qorvo, recipients of US government funding, described their activities. Qorvo is focused on RF, and Intel is focused on high-performance computing with its embedded multi-die bridge (EMIB) technology. The panel admitted that, in the absence of a volume supplier of buildup substrates, the DoD depends on a global substrate procurement strategy.

A session on diversity and career growth provided advice from a panel of experts, including representatives from IBM, Lam Research, Edwards and Cadence. The plenary session covered digital transformation with participation from Intel, TSMC, Yole, Onto Innovation and Samsung. A late-night session focused on Interconnect Technologies for Chiplets with participants from Intel, IBM, Unimicron, TSMC, SPIL and Furukawa Electric. Participants from Taiwan and Japan dialed into the session to discuss topics including embedded bridge, the incorporation of memory in advanced package developments in optical packaging, 3-D packaging and substrates.

E. JAN VARDAMAN is president of TechSearch International (techsearchinc.com); jan@techsearchinc. com.

FIGURE 1. A special panel on packaging challenges. Panelists included (from left) Kevin O'Buckley (Marvell), Raja Swaminathan (AMD), Ming Zhang (Synopsys), Ravi Mahajan (Intel), Sandeep Razdan (Cisco Systems), and moderator Jan Vardaman (TechSearch).

Adapting to substrate shortages. With the continued substrate shortage, companies focused on the potential for a fan-out wafer level package (FO-WLP). Numerous presentations covered several options, with new applications for fanout discussed. SK Hynix discussed the potential for memory applications. IME A\*Star discussed FO-WLP antennain-package (AiP) for automotive radar applications. Researchers at UCLA described their work on FO for micro displays. RFcore discussed FO-AiP for 5G mmWave applications. Amkor, ASE and Samsung presented package options for FO-WLP.

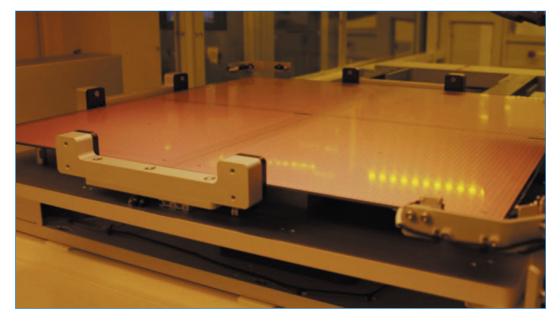

Processing FO in a panel has been proposed as a way to lower the cost by increasing the number of parts with large-area processing. Fraunhofer and the Technical University of Berlin discussed the technology limits of panel processing, describing warpage and die shift as the major issues. Layout adaptation is promoted to overcome die-shift challenges on large panels. Samsung Electronics discussed the reliabil-

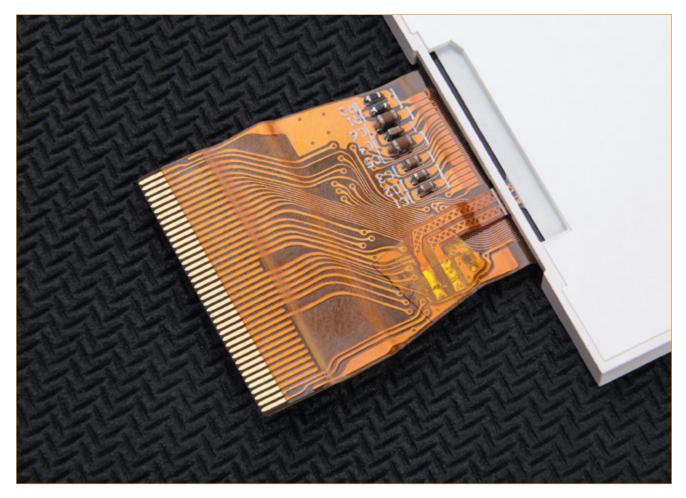

FIGURE 2. The Nepes nPLP 600mm x 600mm fanout panel line reportedly can produce five times as many chips as one 300mm round panel.

ity of the via structure in its FOPLP line. Amkor introduced its 650mm x 650mm panel line. Nepes provided reliability data on FO packages fabricated on its new panel line based on Deca M-Series technology (FIGURE 2). Deca Technologies described 20 $\mu$ m device pad pitch with its M-Series process. The use of adaptive patterning provides a way to handle die shift. Dai Nippon Printing introduced its panel-based RDL interposer with a 2 $\mu$ m pitch semi-adaptive process for chiplet integration.

Several presentations focused on new substrate options, including glass as a substrate and RDL interposers. Developments in glass substrates were introduced with papers from Korea Electronics Technology Institute and Georgia Tech. TSMC introduced its organic interposer CoWoS-R+ technology that replaces the silicon interposer with an RDL structure. The plus indicates the integration of a large amount of highdensity integrated passive devices (IPDs) that serve as decoupling capacitors. The integrated de-cap capacitors suppress the power domain noise and enhance HBM3 signal integrity at a high data rate. Optional silicon connection blocks (bridges) provide high-density die-to-die connections. IBM provided updated work on its direct bonded heterogeneous integration (DBHi) silicon-bridge package, in which the Si bridge is connected to the die and then mounted on the laminate substrate. SPIL provided recent reliability data for its embedded bridge package. Unimicron discussed its hybrid substrate with a buildup film.

**3-D hybrid bonding.** Three years ago, many ECTC papers focused on R&D activities in hybrid bonding. This year, more than 30 papers discussed hybrid bonding process improvements and new developments. While image sensors have been using hybrid bonding for many years, Sony described their recent work to develop 1µm face-to-face bonding and a new thinning process that minimizes Si thickness variation across

the wafer. Adeia's (formerly Xperi) study of the influence of Cu microstructure on the thermal budget shows the possibility of a 20° to 40° reduction in the final anneal temperature. CEA-Leti presented research conducted with Intel on a new die-to-wafer (D2W) collective bonding self-assembly process using water droplets with high alignment accuracy and high throughput. SK Hynix reported the work on wafer-to-wafer (W2S) DRAM stacking for DRAM. Samsung presented several papers on hybrid bonding, including research on controlling bonding voids. AMD described its V-Cache, now in commercial production for servers, desktops and gaming, using TSMC's SoIC process. TSMC described an extension of its SoIC process.

**Co-packaged optics.** Several presentations focused on copackaged optics (CPO). Rockley Photonics introduced a fanout silicon photonics module for next-generation CPO. Rain Tree and IME A\*STAR described a heterogeneous integration package using FO-WLP for a hyperscale data center. IBM Canada, GlobalFoundries and others discussed optical fiber pigtail integration for CPO. Cisco described its vision for CPO and challenges in the use of through-silicon vias, including high warpage, optical fiber coupling, and chip-on-substrate assembly. Reliability requirements were also highlighted. A joint paper from EV Group, Tyndall National Institute, IMEC and Ghent University described a high-speed Si photonic switch with a micro-transfer-printed III-V amplifier. ASE described its CPO assembly.

**Emerging areas.** Presentations also covered additive manufacturing, 3-D printing, developments in packaging and assembly for wearables, and micro LEDs.

Next year's ECTC will be held in Orlando May 30 to Jun. 2.

## The Largest Conference and Exhibition for Printed Circuit Board Design, Fabrication and Assembly in the Silicon Valley

## CONFERENCE: October 4 – 7 EXHIBITION: Wednesday, October 5

## SANTA CLARA CONVENTION CENTER, CA

## **REGISTER NOW**

#### **SPEAKERS**

- ≫ Dan Beeker

- ➢ Tomas Chester

- ≫ Keven Coates

- $\gg$  Rick Hartley

- ≫ Susy Webb

## HOT TOPICS

- $\gg$  Controlling noise

- $\gg$  Design for resiliency

- ≫ loT design

- ≫ RF/microwave design

- ≫ Stackups

## HIGHLIGHTS

- ≫ 40 presentations + 9 Free

- $\gg$  110+ Training hours

- $\gg$  Professional Development Certificate

- ≫ 100+ exhibiting companies

- $\gg$  lunch & reception on exhibition floor

## PCBWEST.COM

## SCHEDULE-AT-A-GLANCE

## TUESDAY OCTOBER 4, 2022

| Time                 | Title                                                                                                                       | Speaker                                    |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 9:00 a.m 10:00 a.m.  | Panel: Where is the Design Profession Going?                                                                                | Mike Buetow, PCEA                          |

| 10:00 a.m 12:00 p.m. | Making Intelligent Material Decisions                                                                                       | Michael R. Creeden CID+, Insulectro        |

|                      | How to Fight Magnetic Noise Gremlins                                                                                        | Keven Coates, Fluidity Technologies        |

|                      | Industry Best Practices for Hardware IP Reuse                                                                               | Stephen Chavez, Siemens                    |

|                      | From DC to AC – Power Integrity and Decoupling Primer for PCB Designers, Situation Today and Outlook for the Future         | Ralf Bruening, Zuken                       |

|                      | Back-to-Basics: Understand PCB Fabrication Processes for Traditional, HDI, and Ultra HDI                                    | Mark Hughes, Summit Interconnect           |