Alternate Reality Gets Real

# <section-header> Prevenuence predandf.com Circuitsassembly.com March 2022

Using the Multi-Tone Technique for PDNs

Too Hot for SI? PCB Design Goes to College So You Want to Buy an EMS

PCEA

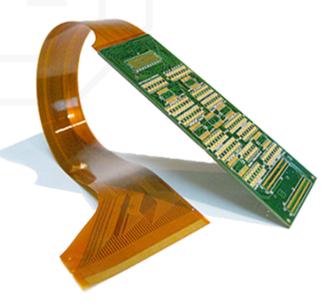

# Flex PCB Assembly & Manufacturing

Get your Custom PCBs exceptionally fast and perfectly tailored to your business needs with our complete dedication to quality and high performance.

### Click to learn more

# Integrated PCB Design, Effortless Collaboration

### Collaborate From Anywhere, Innovate From Everywhere With OrCAD for Teams

Optimize every part of your design process with the only real-time PCB design and data management platform built to scale with you and your team. From automated supply chain insights and constraint-driven, high-speed design and analysis to one-click release-to-manufacturing, OrCAD for Teams is architected to help you work more efficiently and effectively than ever before.

Get OrCAD for Teams >>

# **PROTOTYPES** FROM TAIWAN

# **No Tariffs!** Best Quality and Price!

### Technology:

Up to 50 Layers Any Layer HDI Sequential Lamination Blind / Buried Vias Laser Drilling / Routing Heavy Copper

### Materials:

Fr4 Metal Core Isola Rogers Polyimide - Flex Magtron

www.PCB4u.com sales@PCB4u.com Tel: (408) 748-9600 2986 Scott Blvd., Santa Clara, CA 95054 SAM & ITAR Registered UL E333047 ISO 9001 - 2015

### FIRST PERSON

### 6 THE ROUTE Look up.

Mike Buetow

### MONEY MATTERS

### 16 **ROI**

Domestic opportunities. Peter Bigelow

### 17 BOARD BUYING

X'd out. Greg Papandrew

### TECH TALK

### 18 DESIGNER'S NOTEBOOK

Surface finish change-up. John Burkhert, Jr.

### 20 MATERIAL GAINS

Escaping the *real* real world. Alun Morgan

### 62 GETTING LEAN

The cost of solder. Hom-Ming Chang

### 64 SEEING IS BELIEVING

Unrestrained conversation. Robert Boguski

### 66 TECHNOLOGY FLASHES

Updates in silicon and electronics technology. Binghamton University

### 75 TECHNICAL ABSTRACTS

### DEPARTMENTS

- 8 AROUND THE WORLD

- 14 MARKET WATCH

- 73 OFF THE SHELF

### PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

### **FEATURES**

### 1 IMPEDANCE Cover story

### Rogue Wave Estimation in PDNs Using the Multi-Tone Technique

A new design/analysis method for estimating rogue wave amplitudes is presented that can be compared against the digital chip specs for design verification. by ISTVAN NAGY

### 43 SIGNAL INTEGRITY

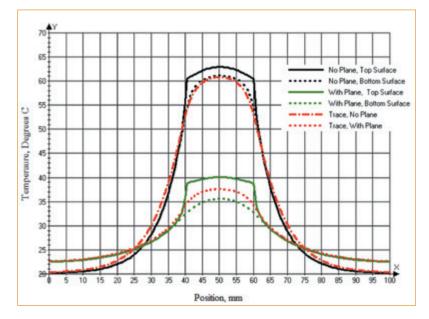

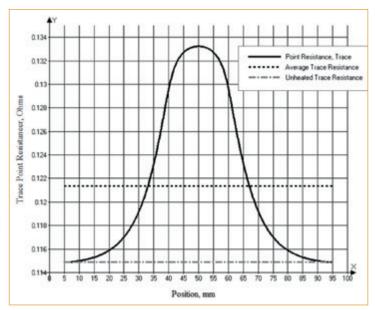

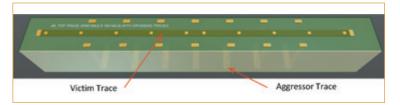

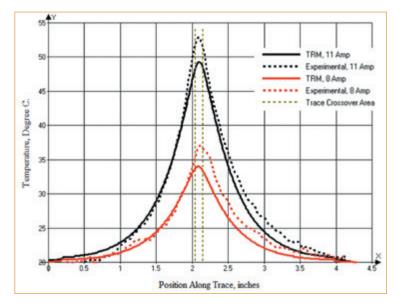

### Does a Heated Conductor Have Signal Integrity Implications?

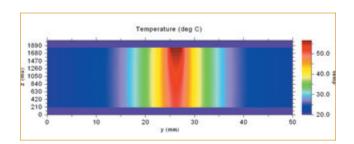

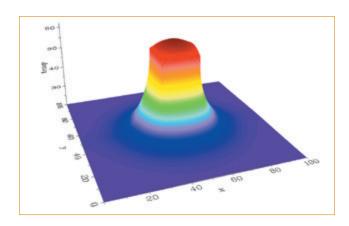

Signal traces internal to the board can – and most assuredly do – change temperature along their length. Therefore, they change resistance. Is that change significant enough to worry? by DOUGLAS BROOKS, PH.D., JOHANNES ADAM, PH.D., and ULISSES CASTRO

### 50 TRADE SHOWS

### Apex Was Live Again. We Should Be Thankful for That.

The annual IPC Apex Expo trade show, traditionally the largest assembly show in the US, was more "expo" than "apex" when it resumed as a live event in San Diego in late January. Here are some highlights. by MIKE BUETOW

### 54 TRAINING

### **Design Engineering: Back to School**

The Rochester Institute of Technology and industry have developed a novel curriculum for teaching PCB design. Chris Banton, director of marketing at EMA Design Automation, and Dr. James Lee, acting chair of the Electrical and Computer Engineering Technology department at RIT, explain what spurred the program and what it hopes to accomplish. by MIKE BUETOW

### 60 M&A

### Planning to Sell Your EMS Business?

If you're an owner planning to sell your EMS business, here are questions to expect from would-be buyers. Consider this a basic primer before striking a deal. by BOB ROSSOW

### ON PCB CHAT (pcbchat.com)

MACK TECHNOLOGIES' MEXICO EXPANSION with WILL KENDALL and OSCAR GONZALEZ

with will KENDALL and OSCAR GONZALEZ

### COLLEGE CURRICULA ON PCB DESIGN

with DR. JAMES LEE and CHRIS BANTON

RUSHPCB

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB ELECTRONIC DESIGN, & QUICK TURN CIRCUIT BOARDS, ASSEMBLY & FULL TURNKEY

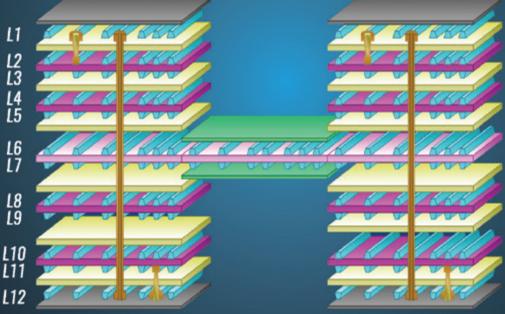

# Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

# When you're in a rush call RUSH PCB

Affordable Pricing • Satisfaction Guarantee • Fast Response • Free Quote • Fast Shipping HDI Boards • Stacked Micro Vias • 2 mil line & Space • Flex & Rigid Flex

### Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL

www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

PCEA PO BOX 807 AMESBURY, MA 01913

### PCEA BOARD OF DIRECTORS

Stephen Chavez, CHAIRMAN Michael Creeden, VICE CHAIRMAN Justin Fleming, SECRETARY Gary Ferrari, CHAIRMAN EMERITUS MEMBERS Michael Buetow Tomas Chester Tara Dunn Richard Hartley Scott McCurdy Susy Webb Eriko Yamato

PCEA.NET

#### THE PRINTED CIRCUIT ENGINEERING ASSOCIATION, INC. BRANDS:

### PUBLICATION

| PCD&F/Circuits Assemblydigital.pcea.net                                                                           |  |

|-------------------------------------------------------------------------------------------------------------------|--|

| WEBSITES<br>PCD&Fpcdandf.com<br>Circuits Assemblypcdandf.com                                                      |  |

| NEWSLETTER<br>PCB Updatepcbupdate.com                                                                             |  |

| PODCASTS<br>PCB Chatpcbchat.com                                                                                   |  |

| EVENTS         pcB West         pcbwest.com           PCB East                                                    |  |

| EDUCATION<br>PCB2Daypcb2day.com<br>Printed Circuit Universityprintedcircuituniversity.com                         |  |

| AWARDS PROGRAMS<br>Service Excellence Awardscircuitsassembly.com<br>NPI Awardscircuitsassembly.com<br>pcdandf.com |  |

| DATABASE                                                                                                          |  |

Directory of EMS Companies.....circuitsassembly.com

PRINTED CIRCUIT DESIGN & FAB / CIRCUITS ASSEMBLY

### STAFF

PRESIDENT Mike Buetow 617-327-4702 | mike@pcea.net

VICE PRESIDENT, SALES & MARKETING Frances Stewart 678-817-1286 | frances@pcea.net SENIOR SALES EXECUTIVE

Brooke Anglin 404-316-9018 | brooke@pcea.net CHIEF CONTENT OFFICER

Chelsey Drysdale 949-295-3109 | chelsey@pcea.net

#### PCD&F/CIRCUITS ASSEMBLY EDITORIAL

CHIEF CONTENT OFFICER

Chelsey Drysdale 949-295-3109 | chelsey@pcea.net

### **COLUMNISTS AND ADVISORS**

Clive Ashmore, Peter Bigelow, Robert Boguski, John D. Borneman, John Burkhert, Joseph Fama, Mark Finstad, Bill Hargin, Nick Koop, Alun Morgan, Susan Mucha, Greg Papandrew, Akber Roy, Chrys Shea, Jan Vardaman, Ranko Vujosevic, Gene Weiner

#### PRODUCTION

ART DIRECTOR & PRODUCTION blueprint4MARKETING, Inc. | production@pcea.net

#### SALES

VICE PRESIDENT, SALES & MARKETING Frances Stewart 678-817-1286 | frances@pcea.net SENIOR SALES EXECUTIVE Brooke Anglin 404-316-9018 | brooke@pcea.net

#### REPRINTS

brooke@pcea.net

### **EVENTS/TRADE SHOWS**

EXHIBIT SALES Frances Stewart 678-817-1286 | frances@pcea.net TECHNICAL CONFERENCE Mike Buetow 617-327-4702 | mike@pcea.net

#### SUBSCRIPTIONS

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. To subscribe, visit pcdandf.com or circuitsassembly.com and click on Subscribe. For changes or cancellations to existing subscriptions: subscriptions@pcea.net

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by Printed Circuit Engineering Association, Inc., PO Box 807 Amesbury, MA 01913. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

© 2022, Printed Circuit Engineering Association, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/ CIRCUITS ASSEMBLY is forbidden without written permission.

It starts with designing an alloy to meet reliability requirements. Next, a chemistry that optimizes how the alloy reflows and solders. And finally, working with the customer to see how PCB design and assembly can optimize performance and reduce costs and defects.

### **Process Expertise**

Mechanical reliability Reflow optimization Reduced material cost Lower energy consumption

### **Innovative Products**

High Reliability Alloys Solder Paste Solder Preforms Cored Wire

### Let's get started.

Alpha's low-temperature soldering (LTS) solutions have revolutionized high volume applications, including conversion from Wave to SMT and from SAC alloys to Low Temperature SMT. Let's work together to find the optimal LTS solution for your process.

www.macdermidalpha.com

### THE ROUTE

MIKE BUETOW PRESIDENT

# The Future of Space is No Longer Up in the Air

TWASN'T LONG ago NASA administrators were lamenting ongoing cuts to the world's leading space agency's annual budget were putting the US at risk of falling behind its competitors.

No one remembers, but in the 1960s the line item for NASA made up more than 4% of the federal US budget. Once a few footprints were made in space, however, the shine was off the moon rock. A decade later, NASA's budget had been slashed by two-thirds in real dollars, and only briefly topped 1% of the federal budget again over the next 50 years.

Today it hovers around 0.5%, which still translates to more than \$20 billion a year in funding. Indeed, the Biden administration proposed allocating nearly \$25 billion to NASA in 2022 to support moon exploration and more.

As craft go up, costs come down. It can cost up to \$400 million to lift some United Launch Alliance ships off the ground. That's one reason why NASA is so interested in its so-called Venture Class of launch vehicles, smaller vessels that carry smaller payloads but lower risks, especially to the bottom line if they end up cone down. These rockets are priced at a few million dollars apiece, chump change, especially for those, ahem, explorers named Branson or Bezos.

More than a dozen companies in the US alone have been launched to deliver humans and cargo above, and NASA has carved out a few hundred million dollars of its budget to support such efforts.

There's a lot going on over our heads. Russia, China, Israel, India, and Luxembourg (!) have joined the US in launching moon missions, and more than a dozen countries have at least 10 satellites now orbiting Earth. More than 4,500 satellites are currently traversing the skies, according to the Union of Concerned Scientists. (See their database here: https:// bit.ly/30Qkv4i.) The skies, it seems, are the new Manhattan.

Jokes aside, space is serious stuff. So serious, in fact, NASA quietly warned one of those private launch providers that its non-geostationary (a fancy word for "moving") orbit satellite system is a risk to the NASA space missions, including manned operations such as the International Space Station. NASA was responding to SpaceX's plans to launch some 30,000 satellites to orbit later this year. For its part, the space agency is tracking about 25,000 objects in orbit (not all are manmade), of which more than 6,000 have a perigee – the point in the orbit of the moon or a satellite at which it is nearest to Earth – of less than 600km. Based on the letter, dated Feb. 8 (www.scribd.com/document/557924666/NTIA-NASA-NSF-letter-to-FCC-regarding-Starlink-Gen-2), NASA looks to be pushing back, citing possible risks to its ongoing missions and even human life.

"SpaceX's Gen2 expansion," the agency wrote, "would more than double the number of tracked objects in orbit and increase the number of objects below 600km over five-fold, without factoring in growth from other proposed constellations. An increase of this magnitude into these confined altitude bands inherently brings additional risk of debrisgenerating collision events based on the number of objects alone. NASA anticipates current and planned science missions, as well as human space flight operations, will see an increase in conjunctions [read: collusions]." Such an increase, NASA asserts, could also degrade the images captured by the Hubble telescope, while also obscuring ground-based telescopes that survey for Earth-bound asteroids. (Two days after the letter was submitted, SpaceX lost nearly an entire fleet of 49 satellites right after launch due to a solar storm. Don't look up, indeed.)

As retired astronaut Paul Lockhart notes, technology drives economics. NASA proposes SpaceX prove out its collision avoidance system as a condition of its launch. Such developments have obvious corollaries to terrestrial uses. Besides sensors, we can expect major advancements in robotics, communications, additive manufacturing (space travelers may need to print their own food), virtual reality, among other technologies, all of which need to be designed and engineered here on Earth.

The future of space is no longer up in the air, but making products – and profits – remains a high-risk venture. Organizations like the Printed Circuit Engineering Association offer the training and guidance from minds experienced in high-reliability electronics design and manufacturing. Join us at PCB East (pcbeast.com) in April in Marlborough, MA, or at one of our local chapter meetings, and take advantage of the printed circuit pioneers.  $\Box$

mike@pcea.net @mikebuetow

# Measure PCB Surface Finishes ENIG, ENEPIG & EPIG

XRF with Automated X-Y table

- Increased Throughput

- Improved Reliability

IPC 4552 A, IPC 4556

### Measuring made easy

www.fischer-technology.com

### **PCDF** People

Bev Christian (left), Doug Pauls, and Jose Servin were presented with Dieter Bergman IPC Fellowship awards.

Nano Dimension named Sean Patterson chief revenue officer. He joined in June 2021 as president of Americas after holding leadership roles in Amazon's transportation and healthcare groups.

Sunstone Circuits added **Debra Coburn** to its management team as human resources manager.

Zuken Vitech appointed Enrique Krajmalnik CEO. He joined Zuken USA in 2020 as vice president of business development and later moved into the Vitech organization as COO.

### **PCDF Briefs**

Altium and MacroFab announced Altimade, a "design with manufacturing" application, is now available to the Altium user community.

On Sept. 1, **Bowman** will formally open a new 20,000 sq. ft. global headquarters in Schaumburg, IL.

**DuPont Microcircuit** and **Components Materials** are collaborating with **Kuprion** to launch ActiveCopper thick film paste products to the electronics industry.

**DuPont Interconnect Solutions** completed a \$250 million expansion at its manufacturing site in Circleville, OH, expanding production of Kapton polyimide film and Pyralux flexible circuit materials.

Nano Dimension is collaborating with TTM Technologies to open an AME NanoLab at TTM's advanced manufacturing center in Stafford Springs, CT.

**RBP Chemical Technology** announced an exclusive partnership with **Schlötter** in Geislingen, Germany.

Ventec's Fullerton, CA, facility is now certified according to AS9100D and ISO 9001:2015.

### It's Official: PCEA Acquires Key Assets of UP Media Group

**PEACHTREE CITY, GA** – The Printed Circuit Engineering Association (PCEA) has closed on its acquisition of the functional assets of UP Media Group Inc., including its industry leading publications and trade shows.

The deal, which was pre-announced during the PCB West conference and exhibition last October, includes the annual PCB West and PCB East trade shows; PRINTED CIRCUIT DESIGN & FAB (PCD&F) and CIRCUITS ASSEMBLY magazine; the PCB UPdate digital newsletter; the PCB Chat podcast series; the PCB2Day workshops and webinars; and Printed Circuit University, the dedicated online training platform.

The deal establishes PCEA as the leading association for printed circuit engineers worldwide, with over 2.5 million engagements annually to printed circuit engineers, designers, fabricators and assemblers.

Upon closing, Mike Buetow has been named president; Frances Stewart has been named vice president, sales and marketing; Chelsey Drysdale has been named chief content officer; and Brooke Anglin has been named senior sales executive.

The staff reports to the PCEA board of directors, which is made up of 10 industry professionals led by chairman Stephen Chavez and vice chairman Michael Creeden.

"We have been looking forward to this day since we entered negotiations with PCEA several months ago," said Mike Buetow, president, PCEA. "We are fired up and ready to engage with our members, starting with PCB East, our first live event as part of PCEA, which takes place in April in Marlborough, MA."

"I cannot believe we finally closed the deal," said Stephen Chavez, chairman, PCEA. "Simply amazing, but I'm more amazed at what we just accomplished from only being in existence for two years and starting from scratch.

"We are extremely excited and very eager to attack this great new adventure. We're even more tenacious and passionate in our eternal quest to collaborate, educate, and inspire for the betterment of the industry. The first upcoming PCEA conference is PCB East. We hope to see you there." (MB)

### Next-Generation Technologies to be Highlighted in PCB East Keynote

**PEACHTREE CITY, GA** – International electronics industry consultant Gene Weiner, fresh off a trip across the Atlantic where he visited several emerging companies, will keynote this year's PCB East conference. Weiner's talk, "From Possibility to Reality," will paint a picture of exciting possibilities in additive manufacturing, materials, equipment, components and other developments that may be in full swing in the next few years.

The PCB East conference and exhibition (pcbeast.com) will return Apr. 11-13, to Marlborough, MA. Weiner's keynote, which is free to all conference and expo registrants, takes place April 12 at 11 a.m.

Gene Weiner

"It's a new day for industry engineers," says Weiner, "facing challenges and opportunities with new tools, products and software at their disposal to create never before possible interconnected packages. A realm of new possibilities in design and manufacturing is being made possible by rapidly emerging advances in a wide variety of additive manufacturing processes of printed circuits and precision components, as well as specialty substrates.

"Looming new technologies, including AI, offer the chance to create new designs, such as precision capacitors *in situ*, odd-shaped precision inductors (in place), precision shielding in place, rapid precise placement of Type 6 or 7 solder pastes permitting higher first-pass yield on assembly of very fine components, and more that could

Take your electronics assembly further, faster.

# We've Got Solutions

Fluid Dispensing & **Conformal Coating**

Plasma Cleaning & Treatment

Selective Soldering

With our technologies, global sales and support teams, and applications expertise, your solutions are here.

www.nordson.com/electronics-solutions

### **CA** People

AIM appointed **Javier Corona** to district sales manager, Northern Mexico.

Altus appointed **Kevin Suen** applications engineer. He has a degree in mechanical engineering from Birmingham University.

APITech named **Matthew Erlichman** quality engineer and supervisor.

Flex named **Rob Campbell** president, Consumer Devices.

Hernon Manufacturing hired Edgar Rosas as country manager for Mexico.

IPC inducted **Joe O'Neil** to the Raymond E. Pritchard Hall of Fame in recognition and acknowledgment of contributions to IPC and the electronics industry.

Koh Young promoted Ivan Aduna to global MES leader. He previously designed test plans at Intel and worked on embedded software systems at Dextra Technologies.

MacDermid Alpha Electronics appointed Karl Pfluke district sales manager of the Southeast, supporting the Alpha and Kester assembly brands.

MicroCare appointed Manuel Gonzalez Eastern Mexico regional sales manager.

Plexus named Steve Frisch (left) president and chief strategy officer and Oliver Mihm chief operating officer.

STI Electronics promoted **Erin Lewis** to quality manager.

### **CA Briefs**

**BEMA Electronics** bought a **Seica** flying probe tester.

**Cicor Group** said discussions are underway to acquire **SMT Elektronik's** company's electronic manufacturing services activities in Germany. SMT Elektronik employs 145 staff in Dresden and had sales of €22.4 million, with a net profit of €1.2 million in fiscal 2020, much of which came from the EMS unit.

reduce re-spins or make faster adjustments.

"Design engineers who are aware of these innovations in equipment, processes, and materials and their capabilities can be more creative. One of the challenges will be to establish standards for newly designed products and their compositions."

In this keynote, Weiner will draw upon his more than a half-century of global firsts and experiences with major inflection points and new product entries into the PCB fabrication and EMS sectors of electronic packaging to introduce and predict the possible and the probable.

"Few people in the world have seen the variety of printed circuit, semiconductor and electronics packaging technologies that Gene Weiner has, and ever fewer are able to put them in the context of how they can be implemented," said Mike Buetow, president of PCEA and conference director, PCB East. "I guarantee attendees will come away with their eyes opened to new possibilities for design and manufacturing." (MB)

### **Draper Team Develops Predictive Design Tool**

**CAMBRIDGE**, **MA** – Draper has developed a predictive design tool that has been tested and validated to show it can predict material failure rates and help determine design requirements for printed circuit boards and similar products.

In tests, engineers found the tool accurately predicted methods to reduce and eliminate laminate crack initiation and propagation on a PCB.

The study, prepared for IPC Apex Expo 2022, was conducted by designing printed circuit boards, using different configurations and materials, and subjecting the boards to environmental stresses and other tests. Using principles of predictive design, engineers developed data sets to guide them. One data set included tests of the PCB materials for such attributes as fracture toughness and thermal conductivity. Another set included detailed design characteristics of the PCB itself.

With the data, the engineers developed a virtual test bed – a finite element analysis computer-aided model – and used it to run scenarios of various PCBs. The FEA model successfully predicted a 50% decrease in internal stress that would reduce or eliminate PCB laminate cracks.

By tweaking the kind of materials and design layouts of a PCB, the team was able to reduce the number, kinds and severity of defects in the board when minor design changes were made.

Wade Goldman of Draper led the team.

"The FEA model allows us to move attributes around to reduce the number and likelihood of cracks in the PCB," Goldman said. "If each design works as expected, PCB designers and manufacturers are no longer limited to manufacturing by trial and error. Instead, they can spend their time evaluating design changes that might be useful in order to reduce defects and not change their processes."

The model arrives at an opportune time for the technology industry, Goldman added. "These days it's all about designing higher density PCBs. As a result, interconnects are becoming smaller, which introduces fragility, and the industry is making more material choices to make higher density interconnects work. You need a predictive design tool to support that effort."

The predictive design tool is expected to provide PCB designers with a model for determining design rules for future products.

"With this new capability, we have taken a big step in being able to manufacture higher quality printed circuit boards." (CD)

### ICAPE Group Acquires Cebisa France

**PARIS** – An ICAPE Group subsidiary has signed an agreement to acquire 100% of Cebisa France, a printed circuit board supplier based in Lisses. The transaction was expected to close at the end of February. Founded in 1996, Cebisa France had sales of  $\in 2.8$  million across its 50 customers in Europe last year.

**Cope Assembly Products** will represent all **Hentec/RPS** in Georgia, Mississippi, Alabama, and Tennessee.

**Dynamic Source Manufacturing** purchased its fourth **Juki** ISM3600 storage tower.

East West Manufacturing is receiving an undisclosed investment from MSD Partners.

**IPC** presented its highest corporate honors to **Apple** and **MacDermid Alpha**.

**Parmi** named **Horizon Sales** manufacturers' representative group of the year.

**Rehm Thermal Systems** named **Hilpert Electronics** distributor for Switzerland.

**Rocket EMS** has begun electronics manufacturing operations in a newly acquired 50,000 sq. ft. facility in Carson City, NV.

Saki's job data conversion function is now available with Fuji surface mount machines.

Scanfil will expand its EMS factory in Wutha-Farnroda, Germany, by 2,200 m<sup>2</sup>, with production estimated to begin in the second quarter of 2022. The existing factory is 4,500 m<sup>2</sup> and employs approximately 270 staff.

**SMTA** is seeking student applications for the \$8,000 Charles Hutchins Educational Grant (https://smta.org/page/hutchinsgrant).

Following a merger announcement between **Tempo Automation** and **ACE Convergence Acquisition**, ACE filed a supplement to its Dec. 15 proxy statement, wherein ACE proposed to extend the date by which the company must consummate its initial business combination from Jan. 30 to July 13.

**Unitron Group** selected **Aegis'** Factory-Logix MES.

Videoton EAS will almost double its production capacity in Stara Zagora, Bulgaria, in the near future.

Waséyabek Development has acquired EMS firm Safari Circuits for an undisclosed sum.

Worthington Assembly is among the companies receiving grants from the Innovation Institute at the Massachusetts Technology Collaborative (MassTech) in an initiative to bring artificial intelligence to businesses across the state.

Yunex Traffic bought two Mek (Marantz Electronics) desktop AOI systems.

Z-Axis invested in an Austin American Technology HydroJet inline cleaner. The deal came about after several months of negotiation and planning.

In a statement, ICAPE Group CEO Cyril Calvignac said, "We are very happy to have signed an agreement with Cebisa France, whose activities will soon be transferred to the teams of ICAPE France. With this new important step, ICAPE Group strengthens its leading position on the French electronic suppliers market." (MB)

### **Element Solutions Acquires HSO Herbert Schmidt**

**SOLINGEN, GERMANY** – Element Solutions acquired HSO Herbert Schmidt, a multinational developer of surface finishing technology and chemistry. Terms of the deal were not disclosed.

HSO focuses on environmentally sustainable products, especially in plating on plastics. In 2021, HSO was certified as a climate-neutral electroplating operation functioning under the values of sustainability and climate protection.

Future results from this acquisition will be reported in Element Solutions' Industrial and Specialty segment. (CD)

# Fire Scuttles Elvia's PCB Site in Loire Valley

**LOIRE VALLEY, FRANCE** – A fire in the early afternoon of Jan. 30 at Elvia's plant here destroyed the printed circuit board fabricator's entire production workshop.

The fire was contained at the end of the afternoon, and no injuries were reported.

A preliminary investigation has been opened by the Orléans public prosecutor's office to determine the origin and circumstances of the fire, which are still undetermined.

All factory activity has been shut down, sidelining the site's 87 employees.

While the Loire Valley plant is being cleaned up, a transfer plan is being prepared to permit production to continue, the company said.

It's unclear how the fire will affect the potential sale of Elvia. In early January, Tikehau Ace Capital announced it had entered into exclusive negotiations to acquire 100% capital of the company in a deal expected to close in the first half of this year.

Elvia was founded in 1976 and has five production sites in France and over 450 employees. (MB)

### Axion BioSystems Acquires M-Solv Manufacturing

**ATLANTA** – Axion BioSystems acquired printed electronics manufacturer M-Solv Manufacturing, a subsidiary of M-Solv Ltd. The creation of a new division, Axion BioSystems Manufacturing, UK, cements the six-year partnership between the companies.

"The need to control the supply chain has never been more important," said Tom O'Brien, CEO of Axion BioSystems. "This vertical integration not only ensures our customers have the products they need to conduct critical biomedical research. It also allows us to advance assay plate technologies more rapidly to meet the increasingly complex scientific demands of our users."

"The M-Solv manufacturing team is proud to have played a role supporting Axion's growth over the last six years," said Phil Rumsby, CEO, M-Solv Manufacturing. "Now, as part of the Axion Group, we are looking forward to working together even more closely to grow this part of our business, as we develop the next-generation of bioelectronic assay consumables. Alongside our biosensor business, we will continue to maintain and grow our strong position in touch-panel devices."

No financial terms of the transaction were disclosed. (CD)

# 0 Avalability

Continued Capital Investments | Seasoned PCB Experts The Ability To Say "Yes" To Your Lead Time Needs

### **The Solution Is APCT**

512.548.7435 | APCT.com

Advanced Technology Cycle Time Speed | Knowledgeable People

#### Circuit Board Solutions Printed APCT Anaheim APCT Orange County APCT Wallingford APCT Global APCT Santa Clara HQ

APCT.com

408.727.6442

714.921.0860

714.993.0270

COUNTRY,

203.269.3311 203.284.1215

### **APCT CAPABILITIES**

### **TECHNOLOGIES**

| <u>RIGID</u><br>Standard:<br>Advanced:<br>Development (NPI only):                       | 2 – 28 Layers<br>30 – 38 Layers<br>40+ Layers |

|-----------------------------------------------------------------------------------------|-----------------------------------------------|

| HDI; BLIND/BURIED/STACKED VIA<br>Lam Cycles:<br>Micro BGA Pitch:                        | Up to 8x<br>.2 Millimeters                    |

| <u>FLEX / RIGID-FLEX</u><br>Standard Flex:<br>Rigid Flex:<br>Rigid Flex HDI Lam Cycles: | 1 – 6 Layers<br>4 – 22 Layers<br>Up to 2x     |

| MES                                                                                     |                                               |

| <u>RIGID</u><br>Standard:<br>2 – 10 Layers:<br>12 - 24 Layers:                          | 15 Days<br>24 Hours<br>48 Hours               |

HDI; BLIND/BURIED/STACKED VIA Via in Pad: HDI:

### 48 - 72 Hours 3 - 15 Days\*

\* Depending upon # of Lam Cycles

FLEX / RIGID-FLEX Flex 1 – 6 Layers: Rigid Flex 4 – 22 Layers: Rigid Flex HDI 2x Lam Cycles

5 - 15 Days 7 - 15 Days20+ Davs

### **QUANTITIES**

LEAD TI

- Mid-Production Prototypes

- Production Orders with offshore solutions offered by APCT Global

### CERTIFICATIONS

- ISO 9001 Certified

- AS9100D Certified

- MIL-P-55110 Certified

- IPC 6012 Class 3 & 3A

- ITAR Registered at all sites

### Printed Circuit Board Solutions

APCT.com

408.727.6442

714.921.0860

714.993.0270

APCT Santa Clara HQ 🔅 APCT Anaheim 🔅 APCT Orange County 🔅 APCT Wallingford 🔅 APCT Global 203.269.3311

203.284.1215

# Global Flex PCB Market to Grow at 9% CAGR Through 2026

**DUBLIN** – The global market for flexible printed circuit boards is projected to reach \$20.3 billion by 2026, growing at a CAGR of 9.2% during 2020-2026, according to Research and Markets.

Double-sided FPCBs are projected to grow at a 9.5% CAGR to reach \$10.4 billion by the end of the analysis period.

Growth in the rigid-flex segment is revised to an 8.6% CAGR for the next seven-year period. This segment currently accounts for 21% of the global FPCBs, says the research firm.

In the global single-sided segment, the US, Canada, Japan, China and Europe will drive the 7.5% CAGR estimated, accounting for a combined market size of \$2.4 billion by the end of 2026.

| NOTHING TO WATCH                                                                                                                                     |      |               |      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|------|

| Trends in the US electronics<br>equipment market (shipments only)                                                                                    | OCT. | % CH/<br>Nov. |      | YTD% |

| Computers and electronics products                                                                                                                   | -0.6 | 0.3           | 0.8  | 5.5  |

| Computers                                                                                                                                            | 1.4  | 0.1           | -2.5 | 1.1  |

| Storage devices                                                                                                                                      | -3.5 | -2.7          | -0.7 | 26.7 |

| Other peripheral equipment                                                                                                                           | -2.0 | -4.1          | 8.4  | 3.7  |

| Nondefense communications equipment                                                                                                                  | 0.7  | 1.0           | -1.4 | 6.3  |

| Defense communications equipment                                                                                                                     | 1.7  | -3.8          | 0.0  | 3.2  |

| A/V equipment                                                                                                                                        | -0.4 | 14.1          | -8.7 | 2.6  |

| Components <sup>1</sup>                                                                                                                              | 1.4  | 0.5           | -0.6 | 6.6  |

| Nondefense search and navigation equipment                                                                                                           | 0.7  | -0.5          | 0.1  | 2.6  |

| Defense search and navigation equipment                                                                                                              | 0.1  | 0.1           | 0.1  | 2.1  |

| Medical, measurement and control                                                                                                                     | -1.1 | 1.1           | 2.0  | 5.7  |

| Revised. *Preliminary. <sup>1</sup> Includes semiconductors. Seasonally adjusted.<br>Source: U.S. Department of Commerce Census Bureau, Feb. 3, 2022 |      |               |      |      |

| US MANUFACTURING INDICES                              |      |      |      |      |      |

|-------------------------------------------------------|------|------|------|------|------|

|                                                       | SEP. | OCT. | NOV. | DEC. | JAN. |

| PMI                                                   | 61.1 | 60.8 | 61.1 | 58.8 | 57.6 |

| New orders                                            | 66.7 | 59.8 | 61.5 | 61.0 | 57.9 |

| Production                                            | 59.4 | 59.3 | 61.5 | 59.4 | 57.8 |

| Inventories                                           | 55.6 | 57.0 | 56.8 | 54.6 | 53.2 |

| Customer inventories                                  | 31.7 | 31.7 | 25.1 | 31.7 | 33.0 |

| Backlogs                                              | 64.8 | 63.6 | 61.9 | 62.8 | 56.4 |

| Source: Institute for Supply Management, Feb. 1, 2022 |      |      |      |      |      |

| KEY COMPONENTS                                                         |                          |                        |                        |                    |                    |

|------------------------------------------------------------------------|--------------------------|------------------------|------------------------|--------------------|--------------------|

|                                                                        | AUG.                     | SEP.                   | OCT.                   | NOV.               | DEC.               |

| Semiconductor equipment billings <sup>1</sup>                          | 37.8%                    | 35.5%                  | 41.4%                  | 50.7% <sup>r</sup> | 46.1% <sup>p</sup> |

| Semiconductors <sup>2</sup>                                            | 30.0%                    | 27.6%                  | 24.4%                  | <b>24.5%</b> r     | 28.3% <sup>p</sup> |

| PCBs <sup>3</sup> (North America)                                      | 1.48                     | 1.25                   | 1.15                   | 1.10               | 1.17               |

| Computers/electronic products <sup>4</sup>                             | 5.26                     | 5.27                   | 5.30                   | 5.34 <sup>r</sup>  | 5.35 <sup>p</sup>  |

| Sources: <sup>1</sup> SEMI, <sup>2</sup> SIA (3-month moving average g | rowth), <sup>3</sup> IP( | C, <sup>4</sup> Census | Bureau, <sup>p</sup> p | reliminary,        | revised            |

### Hot Takes

- Worldwide smartphone shipments were 362 million during the fourth quarter, down 3.2% year-over-year. On an annual basis, the market grew 5.7% in 2021, with 1.35 billion smartphones shipped. (IDC)

- Total semiconductor sales will rise 11% this year, following a 25% increase in 2021 and an 11% increase in 2020. (IC Insights)

- Worldwide tablet shipments amounted to 46 million units during the fourth quarter, down 11.9% year-over-year, posting a decline for the second time since the pandemic began in 2020. (IDC)

- Six million electric cars (battery electric and plug-in hybrid) will be shipped in 2022, up from four million in 2021. (Gartner)

- The overall electronic component sales sentiment index registered 116.5 for January, slightly up from the prior month's results. (ECIA)

- Sales of printed circuit board and multichip module CAD software increased 14.5% year-over-year in the third quarter to \$298.3 million. (ESDA)

- North American EMS orders in December were up 47.1% year-over-year and 13.8% sequentially. Shipments were up 0.9% compared to December in the prior year and 8% sequentially. (IPC)

- Global shipments of traditional PCs (desktops, notebooks, and workstations) reached 92.7 million units during the fourth quarter, up 1% year-over-year. (IDC)

- Global electronics manufacturing survey results show nearly nine in 10 electronics manufacturers report material costs are rising, with an additional four-fifths reporting rising labor costs; 13% of the electronics manufacturing supply chain reports inventory is growing, and one in 10 say inventories from their suppliers are growing. (IPC)

- Global semiconductor sales totaled \$556 billion in 2021, the highest ever annual total and an increase of 26.2% year-over-year. (SIA)

- Device suppliers shipped 30% more IC units to the automotive industry in 2021 compared to 2020. (IC Insights)

- The semiconductor shortage and the Covid-19 pandemic disrupted global OEMs' production in 2021, but the top 10 OEMs increased their chip spending by 25.2% and accounted for 42.1% of the total market. (Gartner)

- Worldwide shipments of foldable phones, including flip and fold form factors, reached 7.1 million units in 2021, up 264% over 2020. Forecasts project shipments will reach 27.6 million units in 2025, a CAGR of 70% from 2020 to 2025. (IDC)

- The supply of NAND flash device controller ICs remains tight, particularly those demanding 55nm and 12/16nm process manufacturing. (DigiTimes)

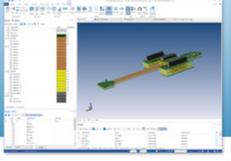

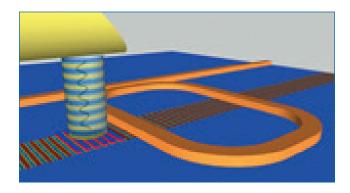

### Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

DownStream's CAM350 and BluePrint-PCB support importation and visualization of PCB designs containing Flex, Rigid Flex or Embedded components. Visualize designs in both 2D and 3D, and easily document complex Flex or Rigid- Flex Stack-Ups for submission to PCB Fabricators.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

- Use DFM analysis to analyze a flex or rigid-flex design for potential fabrication or bend related defects

Use Stack Up Visualizer and Blueprint's Rigid-Flex Stackup template to easily manage and document rigid-flex stackups.

A rigid-flex design in 3D. Shown with layers spread to improve visualization of the layer stackup. Use Rigid-Flex and Inter-layer DFM analysis to analyze flex and rigid-flex designs.

For more information visit downstreamtech.com or call (508) 970-0670

### Get Ready for New North American Opportunities

As governments realize the importance of investing in domestic manufacturing, opportunities are coming for EMS firms and PCB fabricators.

IT TAKES TIME to gain perspective, especially perspective on the industry you are immersed in. In my case, it's been 30 years since I entered the printed circuit board market. During the first six or seven years, it was heady, upbeat times in North America. Growth was a bounty supporting hundreds of domestic fabricators. Materials, supplies and capital equipment were made "locally" in North America. Then, around the new millennium, everything changed.

Suddenly, work headed to Asia, and fabricators contracted at an unprecedented scale to fewer than 200 within a few short years. The collateral damage was a collapse of materials, supplies and capital equipment companies that supported the industry. Even worse was the exodus of skilled talent who sought careers in more promising industries and never looked back. The relatively few companies that survived did so by hunkering down, focusing on a niche, and investing in only the equipment they needed to support their business base, in some cases taking draconian steps that worked short term but eventually led to their demise. Over the first decade-plus of the new millennium, it was depressing to be a North American circuit board fabricator.

However, times change, and with that change, opportunities emerge – finally!

After decades of ignoring reality – and for a variety of reasons and events, many of which have nothing to do with printed circuit boards, or even electronics – government and industry leaders are "shocked" to learn so much of North America's manufacturers are no longer globally competitive and how much more capability and capacity is required for economic and military security. Now that they understand the need to invest in manufacturing, more specifically in electronics manufacturing – everything from chips to bare circuit boards and substrates – opportunities for the North American PCB industry finally may be knocking.

Do we open the door and take full advantage, or ignore it and squander our chance?

To take advantage of the current momentum to expand and enhance North American capabilities and manufacturing capacity may require a radical rethinking, or at least retraining, in how we as an industry operate. The entire risk/reward equation in particular needs to be revisited. After nearly 20 years of operating in a hunkered-down mode to mitigate risk and maximize reward, many in our industry may need to be retrained to break old habits and embrace a paradigm shift the opportunities of the future offer. The first step toward taking advantage of new opportunities may be a brutally honest self-evaluation of what your company does, for whom, and with what resources. Most important is understanding what government or "C-suite" investment in electronics technology may look like and how that will impact your customers. As an example, if chip plants are built in North America, what other electronics manufacturing may now become more cost-effective if done closer to those plants vs. overseas. And, what printed circuit board technology will that increased demand for capacity impact?

With investment in more advanced technology, will new materials and the processing knowhow and equipment be outside current capabilities or comfort zones? Discussions with material suppliers should include a dialogue on what to be aware of; begin experimenting to be better prepared.

If the gap in North American electronics capability points to a specific type of printed circuit board technology that will be in especially high demand, that may be the place to consider increasing capital investment to either add capacity, enhance capability or broaden product offerings to include the growth opportunity. This review should include an estimated capital equipment budget and supporting cash flow, as well as a reality check with current customers to understand if their products and purchasing demands may also be impacted and shifting.

When demand increases, what type of employees will your company need to hire? This leads to workforce development opportunities that currently exist, and in the next few years will expand with an increase in qualified people seeking jobs in electronics. More important, with the emphasis on investing in new capabilities, what talent gap might you have that would prevent being able to produce a new technology? Getting involved *now* may be the best way to ensure having qualified talent when needed.

To take advantage of any opportunity that a reinterest in North American electronics manufacturing may present, it is essential to stay informed and get your team ready. Nothing will happen overnight, but it will happen more quickly than anyone who has become comfortable in the current industry paradigm imagines. We all need to be aware significant new opportunities are finally on the horizon.

After so long operating in a contracting industry segment, we in North America cannot afford to let the coming opportunities be squandered. Opportunity for growth is knocking for us all.

PETER BIGELOW is president and CEO of IMI Inc.; pbigelow@imipcb. com. His column appears monthly.

### A 'No X-Out' Policy is a PCB Cost Driver

A board's level of technology should dictate how often to expect imperfections.

**ONE OF THE** most common questions I get from PCB buyers is, "How many X-outs are acceptable?" Some might say receipt of a PCB manufacturing panel or array with *any* X-outs indicates the supplier cannot maintain a high level of quality.

This is not necessarily the case.

An X-out occurs when a defective board in an array or manufacturing panel of like PCBs has been shipped. The board is literally marked with an X in permanent marker to signify it is flawed.

While a panel or array with zero X-outs is ideal, the board's level of technology should dictate how often to expect this kind of perfection. If the board is a single-, double- or easy four-layer item, then a PCB buyer should expect – in fact, should demand – the manufacturer deliver panels free of defective boards.

However, if it is a higher technology – such as an HDI design – scrap will happen in every manufacturing lot. To expect otherwise is not realistic.

Any experienced PCB supplier knows this custommade item – requiring more than 100 different manufacturing processes – will have a board (or boards) with some sort of rejectable imperfection in every manufacturing lot released to the floor. To address this issue, before the board order hits the production floor, the fabricator will release an overage, depending on the board's technology, to ensure its manufacturing processes yield the number of boards required to fulfill an order.

The more high-tech the board is, the more overage may be necessary to account for any fallout.

For example, let's say 1,050 pieces are released to meet an order requiring 1,000 individual boards. In this case, the manufacturer decides a board's technology will require only an additional 5% in materials overage.

At final QC, the vendor then finds 32 pieces (or about 3%) did not make it through the manufacturing process for various reasons. Those bad boards are scrapped.

Because a 5% overage was produced, 1,018 pieces are good. So, the 1,000-piece order is shipped as promised, and the additional 18 pieces are put into finished spares. Everyone is happy, with most customers not paying any attention to the fallout that occurred within that overage amount.

Sometimes, though, having PCBs delivered in an array or panel format might highlight manufacturing challenges, especially when a customer has a "No X-out" policy.

If you put that same order in a four-up array, then

250 arrays would need to be perfect to meet the 1,000piece requirement. Based on those numbers for that technology, the manufacturer could expect the same percentage of fallout. But boards found at final QC that don't pass muster are "connected" to three pieces that passed with flying colors. This means 32 arrays with an X-out or 128 pieces total (32 x four-up) are not allowed to ship, regardless of their quality.

The vendor must release more overage (about 15%, or 152 pieces, because it's a four-up array) to accommodate the normal fallout that occurs during the manufacturing process for arrays that can't have any X-outs.

Whether your company accepts X-outs or not should be detailed in your firm's PCB fabrication specifications. This information will guide your board suppliers on how much material (overage) they must release – based on their technical capabilities – to fulfill an order.

Here is an example of an EMS company's X-out policy that is clearly spelled out:

"X-outs are allowed. However, not more than 20% of the PCBs in the array can be X'd-out, and no more than 10% of the arrays to be shipped may contain an X-out."

This means if you have, say, a 2,000-piece order manufactured in a 10-up panel requiring 200 arrays to be received, the most you should receive is 20 panels that contain no more than two X-outs each.

Your fabrication specs should also state how X'dout panels are to be received to avoid causing headaches for both receiving and production departments. A statement like this works:

"X'd-out arrays are to be segregated and identified accordingly at time of shipment."

PCB buyers should keep in mind the amount of real estate needed for perfect arrays (no X-outs) means the overall cost of the board will be higher. The adage about not allowing the perfect to become the enemy of the good is applicable here.

Before your company sets its X-out policy, sit down with your manufacturing department. There are ways for an assembler to handle manufacturing panels with X-outs, but the department responsible for shipping quality, finished assemblies should have final say on X-outs.

A rigid "No X-out" policy will likely cost you more without improving the PCB manufacturing process. In most cases, a more flexible approach is warranted.

GREG PAPANDREW has more than 25 years' experience selling PCBs directly for various fabricators and as founder of a leading distributor. He is cofounder of Better Board Buying (boardbuying.com); greg@boardbuying.

### PCB Surface Finishes: When to Change It Up

The primary purpose of surface finishes is to prevent oxidation of the copper prior to soldering components.

**BACK WHEN I** held a soldering iron, we used a mixture of tin (63%) and lead (37%) for the solder (Sn63). The boards had the same coating on the plated holes and surface-mount pads. The application for surface mount is referred to as hot air solder leveling (HASL) and applies to any of the available solder types. The beauty of Sn63 is it has a lower melting point and is eutectic. "Eutectic" means the metal solidifies rapidly over a short temperature range. The benefit is fewer disturbed solder joints and good "wetting," where the surface finish and the solder form a cohesive bond for a reliable connection. You can still buy Sn63 off the shelf at the local electronics store.

On the other hand, lead is a dangerous metal that can cause birth defects and other health issues. The Europeans took the vanguard with the RoHS initiative. If you want to sell electronics products to consumers, the lead content must be the minimum possible – not eliminated entirely but found primarily as a trace element within chips.

SAC (Sn-Ag-Cu): a heroic alloy. Metallurgists all over the world looked for replacement formulas. Tin is

still viable and is generally mixed with small amounts of silver and other elements such as antimony, copper or bismuth. Tin makes up the bulk of the alloy, typically around 95% to 99.3%. If pure tin was used, the results could be problematic. Tin whiskers from dendritic growth present a shorting risk.

Without lead, tin has a much higher melting point and does not solidify as quickly. The double-complication requires a dielectric material that can withstand the higher temperatures without breaking down.

The maximum working temperature of the material is one of the primary selling points. It is known as the glass transition (Tg) temperature. The materials we used in the old days did not stand up to the process, so the entire PCB material set had to be seriously upgraded. Going lead-free raised the reflow temperatures considerably. Boards and components alike have gone green since then.

Exemptions exist where tin-lead is still allowed. Spacecrafts that will eventually burn up on reentry are one such exemption. The goal of RoHS is to reduce the amount of lead that goes into the landfill. Provided the company can certify all its products will be returned to

JOHN BURKHERT JR. is a career PCB designer experienced in military, telecom, consumer hardware and, lately, the automotive industry. Originally, he was an RF specialist but is compelled to flip the bit now and then to fill the need for high-speed digital design. He enjoys playing bass and racing bikes when he's not writing about or performing PCB layout. His column is produced by Cadence Design Systems and runs monthly

FIGURE 1. Pure, non-alloyed metals exhibit crystalline growth as the metal forms branches over time. Environmental conditions can aggravate the process. (Source: NTS Corp.)

the factory for proper disposal, Sn63 coatings on the PCB are permissible. Obviously, consumer products do not get such an exemption.

ENIG: the gold standard. While tin-silver plating is still viable, the "gold standard" is gold. The mainstream alloy is immersion gold over electroless nickel over copper, or ENIG for short. The reason this is a preferred plating is the down-stream process of assembly is more boring without the likelihood of tin whiskers. We like it to be boring when it comes to making goods. Those who study S-parameters also have a fondness for the consistency of ENIG finishes.

This plating is primarily aimed at high-density interconnect fabricators. The process can yield a solderable footprint with via-in-pad situations. Fine-pitch BGAs and other shrunken circuits require microvias. Plating with ENIG will likely improve yields due to the land patterns coming out flatter than with other types of plating. It's also a go-to finish for flex circuits. It plays well with solder mask, making a good base for the following layer.

A note on "black pad": This process defect was a hot topic for a few years. That time has passed. The fabricators worked out the right amount of phosphorus in the nickel to prevent the defect that was more than a cosmetic issue. That concern was laid to rest.

ENIPIG: not too hard, not too soft. Electroless nickel, immersion palladium, immersion gold adds palladium as a physical barrier between nickel and gold. That opens up the process. The main benefit to ENIPIG is the outer layer of gold is soft enough to be a good candidate for wire bonding, while still working well for soldering. The alternative for chip-onboard is a selective soft gold finish: the do-everything finish. When selecting the correct finish, know the constraints. While ENIPIG has an upcharge, it's not as expensive as soft gold or hard gold when used in combination with medium gold. Note medium hardness is geared for solderability, while hard gold creates a more durable contact surface for "gold finger" edge connectors. To meet the specification for HDMI, the gold fingers must withstand 10,000 insertion/extraction cycles.

OSP: a minimalist approach. Organic solderability protectant is a very thin coating consumed by the reflow process. In the factory, we had to be aware of the date codes on boards with OSP. You don't want old boards with this coating.

During design, when reaching back to padstack definitions, the designer must coordinate something extra when using OSP. We had to include a paste stencil opening on our test points when the boards had OSP, or the test points would end up with bare copper. The exposed copper will tarnish over time. None of the other finishes have this requirement.

An IPC specification for OSP (IPC-4555) is on the horizon. Per a report on this publication's website in August 2020, "The goal is to develop performance specifications for hightemperature OSPs, defined as capable of withstanding up to two IR reflows in conjunction with tin-silver-copper (SAC) or tin-bismuth (SnBi) alloys at a peak temperature of 245°-250°C and showing the same wetting balance results at three reflows as zero, with a maximum 20% drop."

This is good news since OSP is well-suited to mass production runs. The micro-thin coating does not hinder solderability. The cost is low, along with the shelf-life. Organic solderability protectant has been around for quite some time with proprietary processes, so it will be beneficial to have a performance standard across the board.

FIGURE 2. ENIG finish with through-hole vias and surface-mount components.

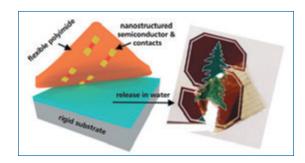

### Alternate Reality is Getting Very Real

The metaverse offers opportunity for escapism and empowerment.

MARKET RESEARCH PUBLISHED last summer suggests the total AR/VR market will top \$700 billion by 2025, suggesting a compound annual growth rate close to 75%. Those are amazing statistics, although we know investment in virtual and augmented reality has surged during the pandemic. Spending on VR has increased, particularly among consumers constrained to stay at home for extended periods. They have time, and they're bored. But professional applications are also expanding quickly in marketing, retail, healthcare and manufacturing.

As a concept, AR/VR is closely connected with another emerging phenomenon: the metaverse. The distinction between the two is quite blurred. The metaverse is perhaps best envisioned as an alternative reality whose scope extends throughout the entire internet and into the real world. Although there will be elements of virtual reality, and a VR headset will provide one means of entering the metaverse, the big tech giants are thinking much bigger. Facebook's parent company has even changed its name to Meta, a clear expression of its ambitions.

We can expect this alternative reality to start becoming accessible through gaming and entertainment applications. People will exist and move around as avatars, go to shops, attend concerts. The chance to style our appearance and create our own reality is a fantastic opportunity for escapism. And who could The opportunities to enhance mental well-being are perhaps even more profound, particularly in the aftermath of the pandemic. The numbers of people suffering from anxiety-related disorders such as agoraphobia are expected to have increased. Those already suffering, having been compelled to stay indoors for extended periods, will likely have experienced setbacks in their battle. The metaverse could greatly expand the prospects for treatment by providing a controlled environment for a patient to enter, move around in, and deal with challenges that are carefully designed to help build confidence.

In a similar vein, metaverse technology can have a democratizing effect on formerly specialized areas of research, like sports performance. Elite sportspeople are known to employ visualization to prepare mentally for high-pressure events. Rehearsing their responses helps fine-tune performance and strengthen the selfcontrol to achieve their ultimate goal. The desire for outstanding achievement is common, yet few can get the right help to use visualization effectively. The metaverse can provide a suitable environment to try it out, with the aid of online courses delivered by your own personal coaching avatar.

continued on pg. 70

blame anyone seeking an escape from the *real* real world?

Important opportunities exist to improve our working lives, however, as well as the quality of services such as healthcare and emergency first response. With the benefit of instant access to building records through the internet, police or firefighters can capture information about the layout, occupants and fire-escape routes within their field of view to preserve their own safety and provide more effective support to those inside.

FIGURE 1. Expect VR headsets to use flex circuits and IMS to reduce size and improve thermal management.

# Rogue Wave Estimation in PDNs Using the MULTI-TONE TECHNIQUE

Effective strategies for calculating rogue wave noise levels. **by ISTVAN NAGY**

For about 20 years, PDN design and analysis focused on the target impedance method. In recent years, additional considerations surfaced about rogue waves, but more as a general discussion. Here we present a new design/analysis method for estimating rogue wave amplitudes we can compare against the digital chip specs for design verification.

Electrical designs must be verified against possible worst-case conditions. For power distribution networks (PDN digital chip supply rail), this is typically done by comparing their impedance profiles against a target impedance requirement. From recent research and publications, we know the target impedance method for analyzing PDN design does not always predict the worst-case noise voltage because different frequency components of the chip supply current load steps can superposition on top of each other. This is sometimes called rogue waves (RW).

The industry has been evaluating different approaches to dealing with RWs: for example, adjusting the target impedance or flattening the impedance profile. Adjusting the target impedance is not sufficient because cases can occur when an adjusted target impedance is already met by the original design's impedance profile, but it still fails with RW noise amplitude that's too large. The whole impedance profile would need shifting down, not just the target impedance line. That is not easy to do. Achieving flat impedance profiles (Q < 0.5) on real digital designs is impractical. For a board designer, a more practical approach is useful to help with the initial component selection and checking the design at the early stage (when the schematic is being drawn) for a pre-layout pass/fail criteria, while not yet considering spatial or post-layout data.

In addition to the target impedance crossing criteria, additional criteria are needed for the designer, namely checking whether the worst-case noise amplitude (RW) is larger than the maximum allowed noise or not by using a crafted worst-case excitation waveform in simulation. We can perform this new type of check by computing the required excitation from the simulated PDN impedance profile. A known method for this is the reverse-pulse technique (RPT) that computes a wide band waveform consisting of rectangular load stepping with specific timing detail. This method requires the use of FFT/IFFT and accurate integral calculus to generate a step response, only correct if the PDN impedance profile was sampled in a linear fashion down to DC. That poses computational resource challenges and is impractical for everyday design projects.

This article introduces new methods. First is the case of implementing the RPT with a log-scale impedance profile that can be computed on 1,000 samples instead of millions of samples, but it is inaccurate. On 1,000 time domain samples (post-IFFT), we could not accurately display both a 100MHz and a 100Hz waveform. We investigate how inaccurate it is, or whether the inaccuracy might be acceptable in practical digital design cases.

The other new method is the multi-tone technique (MTT)

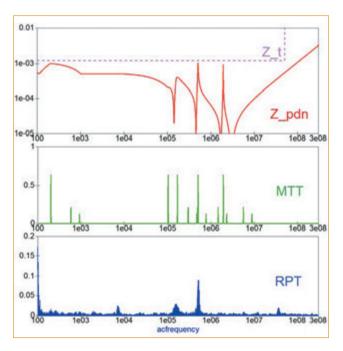

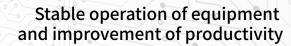

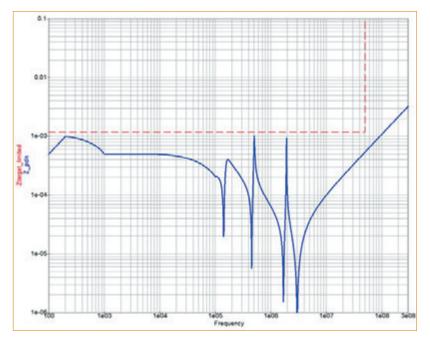

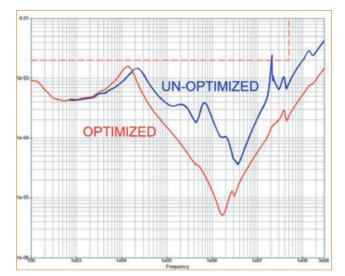

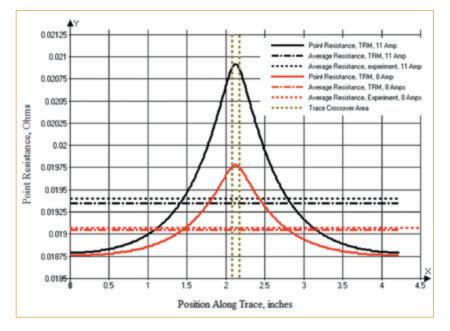

FIGURE 1. Spectrum comparison of MTT and RPT excitation waveforms, both computed from the same impedance profile.

that detects the frequencies of the impedance profile peaks and automatically places periodic excitations to each peak. This works on log or linear scale and does not require FFT or accurate integral calculus, but produces a theoretical signal. It is more like a system vulnerability check, rather than an actual test vector like the RPT.

Both the MTT and RPT seem to "attack" the PDN impedance profile at high-impedance areas, but with different strategies (FIGURE 1). MTT only focuses on peaks. RPT has a complicated distribution partly focusing on peaks, plateaus and other areas. On digital board VDD rails, we don't see multiple sinusoidal excitations. Instead, we have load current stepping/toggling between two levels. From recent publications, we know rogue waves can be created like this: The PDN can be excited with one toggle rate or frequency; it resonates. Then we suddenly change the toggle rate while the system is still resonating on the old frequency on stored energy (forced response), so the voltage response to the old and new frequency are super-positioned to create a larger wave: a rogue wave.

Likely the main requirement of an RW is to present different frequencies at different times, sequentially, relying on recent remnants of resonance from stored energy. The target impedance method only ensures a single frequency component will not cause larger than the allowed voltage disturbance (percentage of VDD). To test and demonstrate different features, phenomena and corner cases, the PDN model had to be tuned differently with different capacitor and VRM parameters.<sup>1,2,3,4</sup>

Further, it will be demonstrated how these complex procedures can be automated with a single software tool: either Keysight ADS or the open-source QUCS. They serve as circuit simulators, SI-simulators and Matlab-like mathematical computational engines in one, allowing us to create custom equations and waveform processing. Normally we create templates, then reuse them in design projects.

The quality factor (Q) describes how under-damped an oscillator or resonator is. It is the ratio of the energy stored in the resonator to the energy lost in one radian of the cycle of oscillation. With higher Q peaks on the impedance profile, the oscillations die out more slowly. This means it oscillates longer, while the load switches the excitation to another resonant frequency that in turn increases the chances of creating a rogue wave. This is why often there is a focus on flattening the impedance profile to prevent the resonances from lasting too long. If we want energy loss to 0.1x in half period (3.14rad), then a Q < 1/  $(1-(0.1^{(1/pi)})) = 1.92$  limit is required. For 0.2x energy remaining, we would need  $Q < 1/(1-(0.2^{(1/pi)})) = 2.5$  limit. That is often achievable with 100nF or larger capacitors, but 0.2x remaining amplitude after half-period is not a guarantee to zero rogue waves. Our simulation template can check for Q factor between capacitor value pairs analytically. This does not compute the RW voltage amplitude; it provides a vague measure for RW probability.

### Q12 = sqrt((ESL1+Lmnt1)/C2)/(ESR1+ESR2)

### The Reverse-Pulse Technique

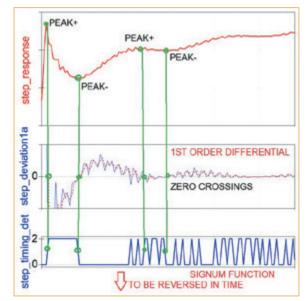

FIGURE 2. Timing extraction in RPT.

A more common method for worst-case voltage response, or rogue wave computation, is the reverse-pulse technique (RPT). This requires

FFT, IFFT, differential, integral and time (vector) reversal computations that would only be correct or accurate when using linear sampling on both the frequency and time domains. With logarithmic frequency sampling, we expect huge inaccuracy or distorted curves, but the spectrum of the excitation waveform aligns exactly with the peaks and high-impedance areas on the impedance profile, so maybe it is not that bad. A linear scale RPT down to DC would require at least 100,000 or, more likely, millions of frequency points to have decent resolution at a wide frequency range that is prohibitive in most simulation tools, especially the free ones. The way RPT is described requires an experienced engineer to assess waveforms, enter data manually, make decisions and use multiple tools.

This could also be automated using post-simulation equations in Keysight ADS or in the open source QUCS.

One attempt to compute a 100,000-point linear scale RPT on QUCS resulted in the simulation freezing at the vector reversal operation. Further simulations were conducted using a reduced bandwidth, reduced sample size, linear sampled RPT between 10kHz and 10MHz, plus a DC point on 1,000 points (10kHz even spacing) run in five minutes on a low-power laptop. Assuming a flat plateau created by VRMs, the DC value was the real value of the lowest frequency sample (10kHz).

The impedance profile as a numeric vector, or "waveform," is processed through several steps to get the voltage response. From the AC circuit simulation result, the complete complex conjugate symmetrical spectrum with DC component had to be constructed at the size of 2<sup>n</sup> or 2,048 samples for the FFT/IFFT to work correctly; that requires a 1,023-point AC simulation. The symmetrical spectrum as a vector was built as [real(Zpdn[0]),Zpdn,0,conj(Zpdn\_rev)]. First we compute the step response:

$[AC-sim] \rightarrow Z_pdn(f) \rightarrow [BW-limit] \rightarrow [symmetrize] \rightarrow [IFFT] \rightarrow Impulse Response(t) \rightarrow [Integral] \rightarrow Step Response(t)$

### **AI OCR Inspection**

Improved detection capability

High performance deep learning model

Vast volume of learning

Continuous performance improvement

# Make Your Process SMART

Xceed

### **AI Auto Teaching**

Reduced teaching time by more than 90%

Chip(C,R), Array Resistor, Transistor, Diode, Tantium, Capacitor, Coil, IC, etc.

Elimination of teaching deviation between operators and reduction of human error

Then detect the voltage fluctuation timing on the step response; then create a toggling load step waveform; then reverse the timing of it (vector reversal). This is the excitation. In the QUCS template, the timing extraction (FIGURE 2) was done by computing the 1st order differential calculus of the step response, then chopping it up with a comparator (using the signum function). In other words, the positive and negative peaks are turned into zero crossings, then vertical edges of a square waveform. Then we can compute the response to that excitation:

$Excitation(t) \rightarrow [FFT] \rightarrow Excitation(f) \rightarrow [Multiply by Z_pdn(f)] \rightarrow [IFFT] \rightarrow Noise(t)$

Finally, we can measure the amplitude of this noise waveform by computing the maximum value minus the minimum value. All RPT equations can be seen in **FIGURE 3**.

Limitations. Sometimes the RPT picks up on the very highfrequency end, but that is not realistic; it's overly pessimistic because every digital board PDN has very high impedance at very high frequency. In fact, they have infinite impedance at infinite frequency. The solution is to decide the frequency range of interest and bandwidth limit of the impedance profile before allowing it to be processed by either RPT, MTT or another technique. This also makes sense for simple targetimpedance checking, as the impedance profile will cross the target impedance line at high enough frequency no matter what. The examples above were between 10kHz and 10MHz, so this issue didn't occur, but on real design verification, we often go up to 50 to 500MHz with the analysis. Very few chip datasheets mention this bandwidth limit. If they do, it is typically 20 to 50MHz. My final QUCS template implements a bandwidth limiting function.

While testing different PDNs with LOG-RPT, especially the smoother ones, it was observed the time domain waveform seems to fly off near the last samples, causing the peak voltage

| Name             |                                                                               |   |

|------------------|-------------------------------------------------------------------------------|---|

| z                | Z_pdn*bw_limit2                                                               |   |

| z1               | [z[1022],z[1021],z[1020],z[1019],z[1018],z[1017],z[1016],z[1015],z[1014       | j |

| z2               | [z[799].z[798].z[797].z[796].z[796].z[794].z[793].z[792].z[791].z[790].z[7    | έ |

| z3               | [z[599].z[598].z[597].z[596].z[596].z[594].z[593].z[592].z[591].z[590].z[5    | έ |

| z4               | [z[399].z[398].z[397].z[396].z[395].z[394].z[393].z[392].z[391].z[390].z[3    | ŧ |

| 25               | [z[199],z[198],z[197],z[196],z[195],z[194],z[193],z[192],z[191],z[190],z[1    | ξ |

| Z_pdn_upp        | conj([z1,z2,z3,z4,z5])                                                        |   |

| zavg             | (integrate(abs(z),1))/1023                                                    |   |

| Z_pdn_ds         | [real(z[0]),z,0,Z_pdn_upp]                                                    |   |

| impulse_response | ifft(Z_pdn_ds)                                                                |   |

| step_response    | cumsum((impulse_response))                                                    |   |

| step_deviation1a | diff(abs(runavg(step_response,3)),acfrequency,1)                              |   |

| step_timing_det  | (1-sign(1*(step_deviation1a-0)))                                              |   |

| r                | 1-0.5"step_timing_det                                                         |   |

| r4               | [r[399],r[398],r[397],r[396],r[395],r[394],r[393],r[392],r[391],r[390],r[389] | ġ |

| r5               | [r[199].r[198].r[197].r[196].r[195].r[194].r[193].r[192].r[191].r[190].r[189] | j |

| step_timing_rev  | [r4.r5.linspace(0.0.624)]                                                     |   |

| excitation       | [step_timing_rev.step_timing_rev]                                             |   |

| excit_freqd      | fft(excitation)/2048                                                          |   |

| voltage_spectrum | Z_pdn_ds*excit_freqd*delta_current                                            |   |

| noise_wf         | (ifft(voltage_spectrum))*2048                                                 |   |

| noise_wf_displ   | real(noise_wf)                                                                |   |

| noise_wf_ampl    | max(noise_wf[10:900]+1)-min(noise_wf[10:900]+1)                               |   |

| noise_rpt        | noise_wf_ampl                                                                 |   |

| pass_rpt         | ((noise_rpt/spec_max_wf)>1)?0:1                                               |   |

| (                | )                                                                             |   |

FIGURE 3. RPT equations.

measured to be higher than the main fluctuations seen throughout most of the waveform. This is likely a computational artifact. We can apply a window function on the waveform and only check the maximum and minimum peak values in the middle 90% of the samples.

In a test done with both QUCS AC-sim and LTspice transient simulation, the windowed version seemed closer to the Ltspice results. There was no VRM in this model, as LTspice does not support S-parameter files. In Ltspice we get a step response curve. By measuring the first two positive and first negative peaks, we can calculate the rogue wave amplitude as described in the original reverse pulse technique. Ltspice uses linear time sampling and no transformations, so it's accuracy can be used as a reference, except it cannot handle measured VRM S-parameter models, so Ltspice is only useful here as a method reference with an RLC PDN model, not for real design validation.

### The Multi-Tone Technique