Al for PCB Designers Signals Move in Spaces, Not Traces Catching Hermes This issue of PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is brought to you by:

# HIGHER DATA SPEEDS WHILE REDUCING COSTS?

Big Data requires high-frequency transmission. At the next DuPont webinar, we'll take a closer look at how DuPont solutions are helping data move at higher speeds, while also reducing energy and the cost of manufacturing.

# REGISTER HERE: https://bit.ly/DuPontWebinar

# **Sierra Circuits**

SIERRA CIRCUITS

presents the new

# **Controlled Impedance** Design Guide

Get the **updated** version of our most **downloaded** design guide!

(https://pages.protoexpress.com/controlled-impedance-design-guide.html)

This design guide empowers designers:

The purpose is to get you on the advanced side of **controlled impedance**.

# What affects impedance

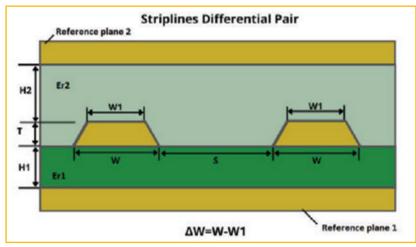

In summary, the impedance of PCB signal traces is affected by:

- · The height of the dielectric layer between the signal trace and the reference plane

- The width and the thickness of the signal trace

- The dielectric constant of a dielectric material

Dielectric materials used in PCB constructions are categorized in two types: copper clad cores and prepregs. The various types of cores and the prepregs usually have different dielectric constants, as specified in the detailed data available from the laminate manufacturer.

TLB, a global leader in the 4th industrial revolution.

# **TRUST 2030**

Good Company in 20 Years, Great Company in 30 Years.

is specialized in manufacturing PCB for semiconductors. By joining World Class 300 in 2018, we have become a company specializing in materials and components leading the fourth industrial revolution. Based on technology and quality, we will establish ourselves as a material parts company that leads not only Korea PCB but also world PCB.

# DRAM Module / SSD Module

IOT / Build-up Board

Semiconductor TEST B'd & 5G Network System

# TLB CO., LTD.

15602) 305, Sinwon-ro, Danwon-gu, Ansan-si, Gyeonggi-do, Republic of Korea Tel.82-31-8040-2096 Fax. 82-31-492-6623 Domestic Tel. 82-31-8040-2071, E-Mail. cmh@tlbpcb.com Offshore Tel. 82-31-8040-2060, E-Mail. will\_shin@tlbpcb.com

# PROTOTYPES IN 4 DAYS FROM TAIWAN

# No Tariffs!

# **Best Quality and Price!**

# Technology:

Up to 50 Layers Any Layer HDI Sequential Lamination Blind / Buried Vias Laser Drilling / Routing Heavy Copper

# Materials:

Fr4 Metal Core Isola Rogers Polyimide - Flex Magtron

# SINCE 1986

www.PCB4u.com sales@PCB4u.com Tel: (408) 748-9600 2986 Scott Blvd., Santa Clara, CA 95054 SAM & ITAR Registered UL E333047 ISO 9001 - 2015 NORTH AMERICA'S LEADER IN HI-TECH QUICK TURN

# ELEVATE YOUR BUSINESS WITH

\$10 MILLION IN RECENT TECHNOLOGY CAPEX INVESTMENTS NIST 800-171 COMPLIANT CYBERSECURITY PROCESSES 250,000 SQUARE FEET SUPPORTING ALL TECHNOLOGIES 4 STATE-OF-THE-ART NORTH AMERICAN FACILITIES

www.summit-pcb.com

### FIRST PERSON

### 6 CAVEAT LECTOR

Military marvel? Mike Buetow

### MONEY MATTERS

### 16 **ROI**

Software and simplicity no longer go hand-in-hand. Peter Bigelow

### **18 FOCUS ON BUSINESS**

What we need isn't always what we want. Susan Mucha

### TECH TALK

#### 20 DESIGNER'S NOTEBOOK

Coping with the noise. John Burkhert, Jr.

#### 24 JERNBERG PI

Keeping the PDN running smoothly. Terry Jernberg

#### 26 MATERIAL GAINS

Positive legacies of the pandemic. Alun Morgan

#### 27 SMART ENGINEERING

Giving the data package processes the heave-ho. Kent Balius

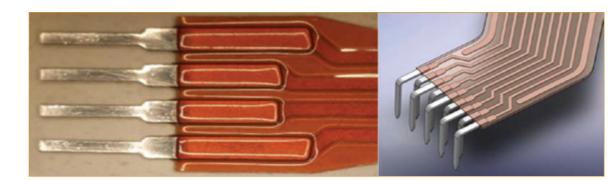

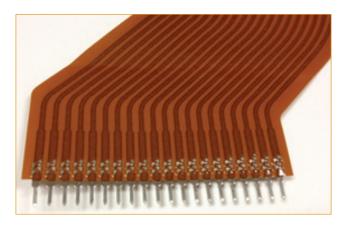

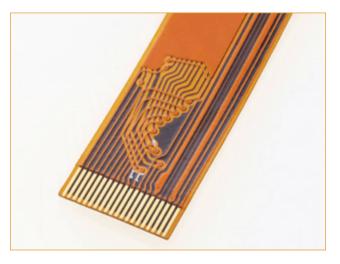

### 28 THE FLEXPERTS

Counting on fingers. Mark Finstad

### 42 SCREEN PRINTING

Get those machines talking. Clive Ashmore

#### 44 **DEFECT OF THE MONTH** Spotting solder spotting.

Bob Willis

### 48 TECHNICAL ABSTRACTS

#### **DEPARTMENTS**

- 8 AROUND THE WORLD

- 14 MARKET WATCH

- 45 OFF THE SHELF 47 MARKETPLACE

# PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

### FEATURES

#### **30 ARTIFICIAL INTELLIGENCE**

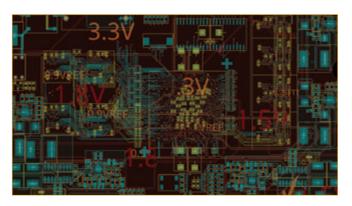

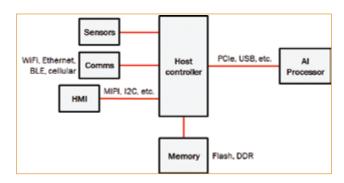

#### The Future of AI is Embedded

2020 brought an explosion of growth in artificial intelligence, but the tech world's interest always seems to be drawn to the software side of AI. What PCB designers need to know to bring AI hardware to the device level. by ZACHARIAH PETERSON

#### 33 ENERGY MOVEMENT

#### Laws of Physics

Signals and energy move in the spaces, not in the traces. by RALPH MORRISON

# STATISTICAL RELATIONSHIPS *cover story*

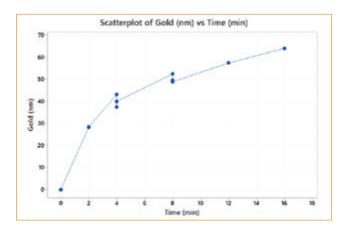

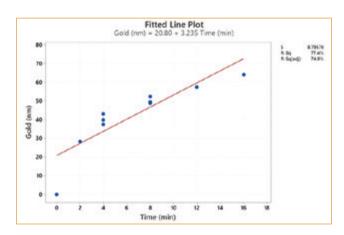

# Application of Nonlinear Regression for Determining PCB Finish Thicknesses

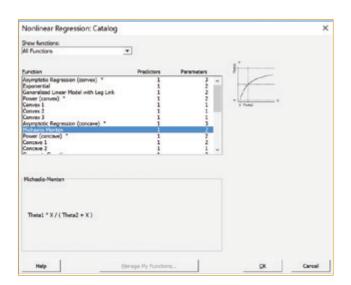

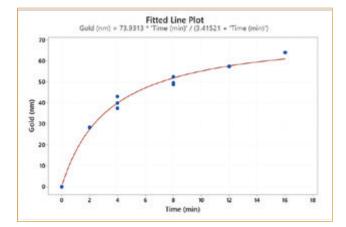

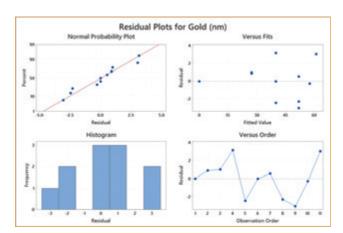

Nonlinear regression is a powerful statistical tool, but it can be challenging to find the appropriate model and starting parameters. Understanding how to choose the proper model and starting parameters is critical. A review of linear and nonlinear regression methods, and a worked example using electroless nickel immersion gold (ENIG). by PATRICK VALENTINE, PH.D.

#### 39 FABRICATION

34

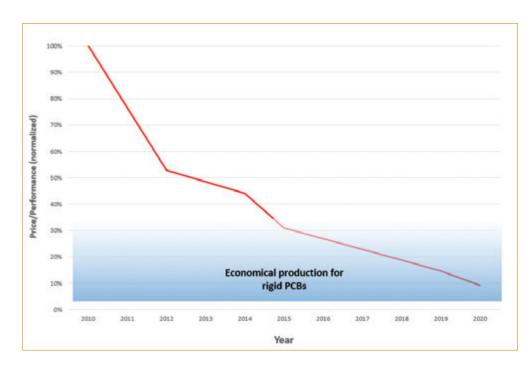

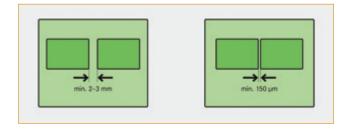

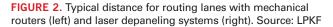

#### **Cost-Efficient Laser Depaneling**

The cost of depaneling based on the effective cutting speed has fallen to approximately one-tenth of what it was a decade ago. Here's why. by PATRICK STOCKBRUEGGER

# IN THE DIGITAL EDITION

The Digital Route The framers unite. by KELLY DACK

### ON PCB CHAT (pcbchat.com)

Electronics Reliability with DOCK BROWN

DuPont's PCB Investments with ANDY KANNURPATTI

#### Industrial Internet of Things (IIOT) with FRANÇOIS MONETTE

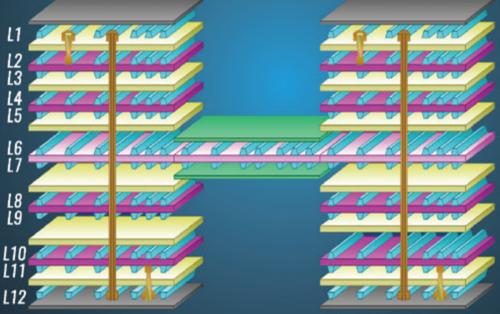

# Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

# When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

# Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

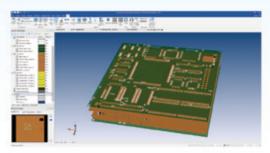

# COMPREHENSIVE PCB DOCUMENTATION

Use 3D Models for Superior PCB Assembly Illustrations

Manage Layer Stackup Design and Materials

# BluePrint PCB

BluePrint automates the PCB documentation process, creating comprehensive electronic drawings to drive fabrication.

of imported CAD data as a 3D PCB

Lowers documentation cost and time

Increases documentation detail & accuracy

Shortens PCB design cycles

Reduces documentation time by 60-80%

# downstreamtech.com • (508) 970-0670

©2020 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

# PRINTED CIRCL **DESIGN** & FA pcdandf.com

circuitsassembly.com

### **EDITORIAL**

EDITOR IN CHIEF Mike Buetow 617-327-4702 | mbuetow@upmediagroup.com

SENIOR EDITOR Chelsey Drysdale 949-295-3109 | cdrysdale@upmediagroup.com

DESIGN TECHNICAL EDITOR Pete Waddell

EDITORIAL OFFICE P.O. Box 470, Canton, GA 30169

#### PCD&F CONTRIBUTING EDITORS

Akber Roy, Peter Bigelow, John Burkhert, Mark Finstad, Bill Hargin, Nick Koop, Greg Papandrew

CIRCUITS ASSEMBLY CONTRIBUTING EDITORS AND ADVISORS Clive Ashmore, David Bernard, Robert Boguski, John D. Borneman, Joseph Fama, Susan Mucha, Chrys Shea, Jan Vardaman, Ranko Vujosevic

# PRODUCTION

ART DIRECTOR AND PRODUCTION blueprint4MARKETING, Inc. | production@upmediagroup.com

# **SALES**

SALES DIRECTOR Frances Stewart 678-817-1286 | fstewart@upmediagroup.com

SENIOR SALES ASSOCIATE Brooke Anglin 404-316-9018 | banglin@upmediagroup.com EXHIBIT SALES

Frances Stewart 678-817-1286 | fstewart@upmediagroup.com PRINT/FLECTRONIC REPRINTS

banglin@upmediagroup.com

### SUBSCRIPTIONS

For changes, additions or cancellations: subscriptions@upmediagroup.com

# **UP MEDIA GROUP, INC.**

PRESIDENT Pete Waddell

VICE PRESIDENT. SALES AND MARKETING Frances Stewart

VICE PRESIDENT. EDITORIAL AND PRODUCTION Mike Buetov

DIRECTOR OF GROUP SHOWS

Alyson Corey | acorey@upmediagroup.com

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. For others, annual Subscription Rates in U.S. funds are: \$80 (U.S. and Canada), \$145 (all other countries). Single copy price is \$8.50. All subscription and single copy orders or inquiries should be directed to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169, email subscriptions@upmediagroup.com. Photocopies and issues on Microfilm/Microfiche (16mm, 33mm or 105mm) are available from University Microfilms International, 300 N. Zeeb Rd., Ann Arbor, MI 48106, Telephone 313-761-4600.

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by UP Media Group Inc., PO Box 470 Canton, GA 30169. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

Periodicals postage paid at Canton/Ball Ground, GA, and additional mailing offices. © 2021, UP Media Group, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/CIRCUITS Assembly is forbidden without written permission.

Postmaster: Send address changes to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169.

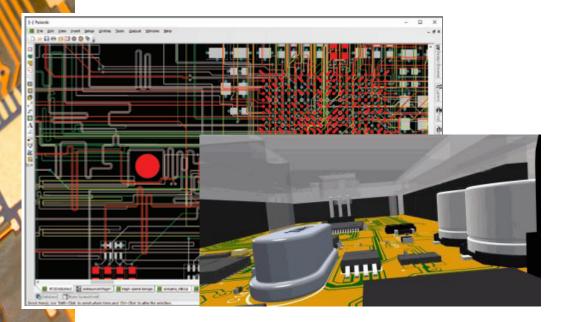

# Pulsonix PCB Design Software

# PCB design done right

# New Version 11.0 Increases Speed up to 80%

Multi-threading and GPU processing in this new release create a gigantic leap in speed, dramatically reducing the time it takes to perform many PCB design operations, such as Design Rule Checking (DRC), Copper Pouring, and Gerber generation. That's PCB done right!

# **Advanced PCB Design Features**

- Intuitive placement and routing

- Dynamic copper pour

- Full rules engine for automatic DRC

- High-speed design rules

- Heads-up display length matching

- Rigid-Flex, embedded components, and chip-on-board

- Revision control and PLM integration

Try Pulsonix yourself at pulsonix.com/trial

### CAVEAT LECTOR

MIKE BUETOW EDITOR-**IN-CHIEF**

# In Defense of Diversity

#### UNITIONS ARE COOL AGAIN.

Well, maybe they always were. But the emphasis by North American manufacturers on procuring defense contracts has perhaps never been greater.

In the throes of the dotcom meltdown of late 2001 to early 2003, when China and Taiwan hoovered up the vast majority of the Western PCB market, forcing those hardy remaining souls to repurpose their business plans, the Pentagon became an unwitting savior. Manufacturer after manufacturer pivoted from the "3Cs" (computers, communications, consumer) to CET&I (military communications, electronics, telecommunications, and intelligence technologies). They eschewed past complaints of onerous red tape and sprung for the certifications to elbow their way into the Pentagon supply chain.

There wasn't much choice at the time. It was military or bust.

Going back to 2001, the United States made about 45% of the world's electronics equipment. Defense and related high-rel sales made up less than 10% of the US domestic fabrication market, which at the time was coming off a record year at around \$11 billion in production output spread across 650 or so facilities.

We all know what happened.

But about that cure. As we reported in last month's digital edition ("US Defense Suppliers Have Begged for Help. A Pandemic Helped Them Get It"), 145 of the 202 printed circuit board facilities in the US as of 2017 supplied the US Department of Defense in some manner.

My concern is that North America might put all its eggs in one basket. This is more an issue for fabricators than assemblers, since the former is less automated and requires more skilled labor hours per \$1 million of product shipped. Also, the workforce is aging faster on the fab side in the West, and it's generally more difficult for fabricators to recruit new engineers and operators, as the industry as a whole and the companies are smaller, and the opportunities for career growth are fewer. Quick swings in demand can truly hamstring a company in the short-term, and many board shops don't have access to enough capital to sustain long downturns.

Despite the significant hoops, there's no question military work holds appeal. The end-customer pays. The margins are relatively steady. There is always the promise of future business, even if the demand volume tends to be somewhat administration-dependent.

I recall a warning IBM economist Phil Swan made in 2001 at an IPC TMRC meeting. In tough times, he said, governments look inward, which could further upset the supply chain. "Most legislators tend to be provincial when push comes to shove. Only 40% of the US Congress has a passport. They're not in touch with the rest of world any more than they have to be. The majority haven't served in a war and don't have that experience. It wouldn't take a lot for them to shut the door and [hurt] economic globalization." How prescient does that sound today?

At that time, the North American fabrication market was still a \$11 billion entity. Today it's less than a third of that. My best estimate pegs the Defense Department procurement of printed circuit boards at a little over \$1 billion annually. That's not far off where it was 20 years ago.

As such, I admit to being concerned when I see so many companies focusing their efforts on the A&D market. Commercial aerospace, as we've seen, is the definition of boom/bust (absolutely no pun intended. Seriously.). Military is steadier, but less so than generally appreciated. It's not uncommon for the CET&I budget to gyrate 10% in either direction year-over-year.

For those still doubting, keep this in mind: Just 10 years ago, in fiscal 2011, the US defense budget for CET&I was \$17.7 billion. Two years later, it was \$13.6 billion, a reduction of almost 24%.

Is your business ready for that?

mbuetow@upmediagroup.com

@mikebuetow

P.S. We have three great webinars coming up in the next two months: Chrys Shea on screen printing, Greg Papandrew on reducing bare board procurement costs, and Dr. David Bernard on getting the most from your x-ray inspection system. Visit pcb2day.com for details.

# Surface Mount Intelligence

# **New** from Europlacer.

Two ground-breaking modules that boost our atom placement range.

europlacer.com/new-modules

### **PCDF** People

The best technical conference paper of IPC Apex Expo 2021 is "Signal Integrity, Reliability, and Cost Evaluation of PCB Interlayer Crosstalk Reduction" by Sarah Czaplewski, IBM.

Elmatica named **Craig Hay**wood senior technical advisor. He spent the past 14 years at Amphenol Invotec.

Hirose Electric USA named **Shinya (Sid) Tono** president and COO.

IPC inducted Karen McConnell into its Hall of Fame, given to individuals who have provided exceptional service and advancement to IPC and the electronics industry. McConnell

supports numerous IPC standards development committees, including the Land Pattern Committee, Design for Excellence (DFX) Subcommittee, Generic Requirements for Digital Twin Task Group, CFX Subcommittee, Terms and Definition Committee and Electronics Documentation Committee.

Orbotech named **Avi Greenberg** general manager Americas and vice president sales.

### **PCDF Briefs**

Autodesk and SnapEDA have partnered to release a new app for Fusion 360.

**Bittele Electronics** updated its *DFM Handbook* and *DFA Handbook*. Both detail best practices for printed circuit board fabrication and assembly.

**Calumet Electronics** announced its SBA certification as a HUBZone business. Calumet also won the **IPC** Peter Sarmanian Corporate Recognition Award for support of individuals through technical and management programs.

The Design Automation Conference and Semicon West have been rescheduled to Dec. 5-9.

The **ExpressPCB** Plus PCB Design Suite (ExpressSCH Plus and ExpressPCB Plus version 3.0) now includes integrated search and download for components using **SnapEDA**.

High data throughput and innovative thermal management may lead to a revolution in systems design that places the burden of electronics cooling on the enclosure more than on the card.

**IDEX Biometrics** signed an agreement with **MFLEX** to mass produce circuit boards for biometric payment cards.

# DuPont to Acquire Laird in \$2B+ Deal

**WILMINGTON**, **DE** – DuPont has entered into a definitive agreement with private equity firm Advent International to acquire Laird Performance Materials for \$2.3 billion, which will be paid from cash on hand. The transaction is expected to close in the third quarter, subject to regulatory approvals and other customary closing conditions.

Laird provides high-performance electromagnetic shielding and thermal management, as well as performance components and solutions that manage heat and protect devices from electromagnetic interference. It has a workforce of more than 4,300 employees with a global network of 11 manufacturing sites in North America, Europe, and Asia and 2020 revenues of \$465 million.

The transaction brings together DuPont's films, laminates and plating chemistry with Laird's electromagnetic shielding and thermal management solutions.

"The acquisition of Laird Performance Materials is a significant step in advancing DuPont's strategy to grow as a global innovation leader and premier multi-industrial company," said Ed Breen, executive chairman and CEO, DuPont. "Laird is a strategic and complementary addition to the electronics and industrial business, and our applied material science expertise, together with Laird's industry-leading application engineering capabilities, further strengthens DuPont as an essential partner for major electronics OEMs and manufacturers."

DuPont expects to realize approximately \$60 million in pretax run-rate cost synergies by the end of 2024, the majority in the first 18 months post-closing. The estimated one-time cost is approximately \$40 million. (CD)

# EC Clears TBBPA from RoHS Restriction List

**BRUSSELS** – The European Commission published the final report on the study to support the review of the list of restricted substances and to assess a new exemption request under RoHS 2 on Feb. 11. The report includes assessment of seven substances, including Tetrabromobisphenol A (TBBPA), for possible restriction.

BSEF, the International Bromine Council, notes the recommendation of "no restriction" on reactive uses of TBBPA (for example, in printed circuit boards), which reflects the low risk of this application in terms of exposure and end-of-life treatment under controlled conditions.

"The study authors did not follow their updated methodology, which states publicly available data should be used for a substance when it's available," said Kevin Bradley, Ph.D., secretary general of BSEF. "We believe available data in the TBBPA REACH dossier leads to a different conclusion: no significant risk under current use conditions."

The report recognizes the need to wait for the finalization of the REACH evaluation of TBBPA, due later in 2021. The report also highlights the difficulty in substituting TBBPA in both its reactive and additive applications.

"The report bears out what we have also seen in a recent study on the impact of BFRs on WEEE plastics recycling by consultants SOFIES." The SOFIES report noted the potential for regrettable substitution and impacts on WEEE plastics recycling with other flame retardants.

BSEF welcomed the EC disclaimer. "It is very helpful to have this disclaimer in place given the serious concerns that we and other stakeholders have over the way the Oeko Institut executed the studies," Bradley said. (CD)

# US EPA Prohibits PIP (3:1) in Electronics as of Mar. 8

**WASHINGTON** – As a final rule, the US Environmental Protection Agency is prohibiting the processing and distribution of phenol, isopropylated, phosphate (3:1) (PIP (3:1)) in electronics as of Mar. 8.

There are some exceptions to the prohibition: for example, for new and replacement parts for automotive and aerospace industries. However, there are no electronics

# **Advanced Technology Capability Does Not Come From Wishful Thinking**

All Facilities Furnished With Cutting-Edge Equipment. All Facilities Deliver Extraordinary Engineering. All Facilities Ready To Say "Yes" to The Next Level of Technology.

Advanced Technology | Cycle Time Speed | Knowledgeable People

# 512.548.7435 | APCT.com

Printed Circuit Board Solutions

APCT.com

APCT Santa Clara HQ 408.727.6442

APCT Anaheim 714.921.0860

APCT Orange County 714.993.0270

APCT Wallingford 203.269.3311

**APCT Global** 203.284.1215 **IMI** has installed a UCE (Universal) alkaline etching machine.

A new **iNEMI** project reports benchmark new and emerging test and measurement methodologies for 5G/mmWave materials.

L3Harris launched a 3-D printed RF circuit at the International Space Station, built with a Nano Dimension printer.

**Lumentum** raised its offer for **Coherent** to \$6.9 billion, part of a three-way takeover battle for the laser firm.

**Molex** has received a US patent for a grid array connector system. The novel connector has conductors from cables directly terminated to a PCB.

**MTS Systems** announced that, based on the preliminary voting results, its shareholders have approved adoption of the previously announced merger agreement with **Amphenol**.

**Rogers** announced the release of its 2021 ESG Report, which details the company's environmental, social and governance (ESG) strategies and commitments.

**Royal Circuit Solutions** installed more than \$2 million worth of new printed circuit manufacturing equipment and expanded its PCB plant.

**Ventec's** facility in Kirchheimbolanden, Germany, is now certified according to AS9100D (DIN EN 9100).

Zero Defects International and Skyla announced strategic plans to offer PCB frontend CAM services throughout continental Europe and the United Kingdom.

### **CA** People

ACL Staticide named **Daniel Kaiser** to direct sales and marketing. He replaces **Tony Banks**, who retired after 33 years with the company.

Advanced Precision Distribution named **Tom Seratti** president. He has more than 40 years of experience in executive and sales management positions at ITC Electronics,

Zack Electronics, Marshall Industries, Avnet, SPI Westek and OK Industries.

AIM Solder appointed **Frederik Rostami** Automotive business manager.

Balver-Zinn managing director **Gregor** Jost passed away.

IPC presented three volunteers with Dieter Bergman IPC Fellowship awards: Michael Ford, Jan Pedersen and Peter Tranitz. industry exceptions, says IPC.

The EPA's final risk management rules to reduce exposure to five persistent bioaccumulative and toxic chemicals (PBTs) went into effect Feb. 5.

PIP (3:1) is used as a plasticizer; a flame retardant; an anti-wear additive; or an anti-compressibility additive in hydraulic fluid, lubricating oils, lubricants and greases, various industrial coatings, and in adhesives and sealants, says IPC. PIP (3:1) is also used in plastic-containing materials that are used to form tubes, harnesses, cables, sleeves, gaskets, and covers of parts – parts used in electrical or electronic products.

IPC seeks member input on the EPA final rule, requesting information on how the final rule may adversely affect supply chains for electronics manufacturers. To provide input, contact Kelly Scanlon, EHS policy and research director, at kellyscanlon@ipc.org. (CD)

# East West Goes North, Nabs Varitron

**ATLANTA** – East West Manufacturing announced on Mar. 10 it has acquired Varitron, an electronics manufacturing services provider based in Montreal. Financial terms were not disclosed.

Varitron was founded in 1991 and operates four facilities in the Montreal area. After the deal closes, Varitron will maintain its Montreal leadership team.

The deal was financed by Heritage Growth Partners.

"We are excited to partner with Varitron to expand our integrated design, manufacturing and distribution services into Canada," said Scott Ellyson, co-founder and CEO, East West. "Varitron has an extraordinary reputation for putting customers first and has an established presence for innovation in a variety of high-growth sectors such as medical, industrial, telecommunications and defense. Varitron allows us to offer our customers even greater nearshore, higher-mix, lower-volume, quickturn electronic manufacturing services. With the addition of Varitron's rapid prototyping and strong R&D capabilities, and our collective design, manufacturing and supply chain capabilities, we can support customers from product inception to full-scale production on a global basis."

Varitron has annual revenues in the range of \$100 to \$125 million, CIRCUITS ASSEMBLY estimates, putting the combined entity at around \$250 million. (MB)

# ITAC Software Acquires Cogiscan

**MONTABAUR, GERMANY** – iTAC Software will acquire 100% of the shares of Cogiscan for an undisclosed sum, the company announced in mid-February. Cogiscan, founded in Bromont, Quebec in 1999, provides factory automation software for the electronics manufacturing industry. It will continue to operate independently after closing.

iTAC, a subsidiary of the Dürr Group, cited Cogiscan's expertise in Industry 4.0 as an impetus for the deal.

"Digitalization is one of the Dürr Group's core competences and offers great potential for growth. With the acquisition of Cogiscan, we will be adding a strong team of experts and key technologies to the digital factory, which is a cross-divisional virtual organization for joint development of digital products," said Peter Bollinger, CEO, iTAC.

Cogiscan has more than 450 customer sites across 50 countries. The two companies have been collaborators for more than 10 years, with Cogiscan supplying machine data to iTAC's MES for corporate customers. (MB)

# OEP Takes 30% Stake in Cicor

**BRONSCHHOFEN, SWITZERLAND** – One Equity Partners has purchased HEB Swiss Investment's shares in EMS firm Cicor Technologies for an undisclosed sum. The closing of the transaction is subject to customary regulatory approvals.

HEB Swiss Investment had been a major shareholder of Cicor Group since March 2009 and held approximately 29.35% of the shares as of Dec. 31.

OEP is a middle market private equity firm with more than \$8 billion in assets.

# Process or product problem? Datest can help.

Datest now features fast, high-energy microfocus CT services for anyone who wants to know why something broke, stopped working, won't start working, or never worked.

Test Engineering. Failure Analysis. Answers.

47810 Westinghouse Drive • Fremont, CA 94539 Phone: 510-490-4600 • Fax: 510-490-4111 Email: Info@datest.com • Website: www.datest.com

CalcuQuote promoted Alex Pinell (left) to account manager, focusing on clients in eastern North America. She joined Calcu-Quote in April 2020. Also named account manager is Marisol Cajigal (center) in Madrid, who will concentrate on Europe, and Jordan Lawrence, who will focus on central and western North America.

iNEMI appointed **Dr. Shekhar Chandrashekhar** chief executive. He was most recently operations manager of Smart Manufacturing Innovation Centers (SMICs) for the Clean Energy &

Smart Manufacturing Innovation Institute (CESMII). He began his career as a member of technical staff at AT&T Bell Labs and held several management positions with Bell Labs/Lucent Technologies/Alcatel-Lucent, where his responsibilities spanned supply chain and network solutions. Shekhar holds a doctorate in mechanical engineering from Concordia University.

Kurtz Ersa added **Andrew Hoggard** to its field service engineering team in support of the US and Canada.

Yusaku Kono and Jon Vermillion were presented with IPC President's Awards. Kono serves on the Connected Factory Initiative Subcommittee, the J-STD-001 and IPC-A-610 Automotive Addendum Task Group, the High Voltage Cable Task Group, and the WHMA A-610 training committee. Vermillion co-chairs the IPC-J-STD-001 committee and IPC-J-STD-001 training committee.

TTI named Mike Morton chief executive.

Yamaha Motor appointed Michael Helin to senior automation engineer of Robot Operations FA.

### **CA Briefs**

A broad coalition of 17 tech, medical, auto, and other business groups urged President Biden to work with Congress to fully fund domestic semiconductor manufacturing and research provisions established in the recently enacted National Defense Authorization Act (NDAA). The letter also calls on leaders in Washington to enact an investment tax credit to help build and modernize more semiconductor manufacturing facilities in the US.

ACC Electronix purchased a Nordson Dage Assure component counter and a laser marking machine.

The company also owns Spartronics and Primus Technologies. (CD)

# **Virtex Acquires EMS Firm Altron**

**AUSTIN**, **TX** – Virtex continued its growth by acquisitions in March with the purchase of Anoka, MN-based Altron Inc. Financial terms were not disclosed.

Altron, not to be confused with company of the same name once located in Wilmington, MA, has a single facility outside Minneapolis, where it focuses on regional defense and medical customers. It was founded more than 45 years ago and specializes in high-mix, low-volume production.

In a press release, Brad Heath, CEO, Virtex, said, "Altron extends Virtex's geographic reach further into the Midwest medical, aerospace and defense corridor, enhancing our relationships with key customers we service in other regions. Altron also brings expanded expertise in medical device manufacturing to Virtex." (MB)

**Chem3** named **Phoenix United Associates** exclusive representative of its ElectroJet digital printers.

China pledged to boost spending to drive research into cutting-edge semiconductors and AI in its latest five-year targets, laying out a technological blueprint to vie for global influence with the US.

**Cogiscan** named **Danutek** to handle sales in Eastern Europe.

**Dixon Technologies** is looking for land in the Kolar, Bengaluru Rural and Ramanagara districts to set up an electronics manufacturing unit.

**Eastek** is opening a manufacturing facility in Fresnillo, Zacatecas, Mexico.

**EMD Performance Materials** announced an expanded focus on the US electronics business and a new name in the US: **EMD Electronics**.

Foxconn and Fisker will develop an electric vehicle, part of the manufacturer's efforts to boost its automotive capabilities.

**IPC** unveiled an ESG for Electronics Initiative to develop guidance for electronics manufacturers on an industry-specific approach to ESG (environmental, social and governance) practices and reporting and to develop aspirational goals that the industry is working to achieve.

**Hentec** named **BTU** exclusive distributor for products in Asia.

The Indian government has started inviting applications for the second round of largescale electronics manufacturing under the production-linked incentive scheme, with focus on electronic components like motherboards and semiconductor devices.

Electronic components supplier Infinite Electronics has been acquired by Warburg Pincus.

**Jaltek** purchased a **Takaya** APT-1400F flying probe tester. Kolb Cleaning named Quiptech distributor in Mexico.

**Micropac** is eyeing a larger facility and a possible HQ move in Garland, TX.

Mycronic will offer Aegis Software's FactoryLogix software solution with its K-Series 3D AOI equipment.

**NEOTech** partnered with **Numerica** to provide new 3D radar for C-UAS and short-range defense missions.

Next Generation Manufacturing Canada (NGen), a Canadian NGO, is investing \$4.9 million into a business consortium led by aerospace technology company MDA to apply advanced manufacturing technologies such as robotics in electronics assembly.

**Oppo** has begun test production at its new smartphone assembly plant in Istanbul, which is currently under construction, according to reports.

**Pegatron** has leased a 420,000 sq. ft. industrial facility in Chennai, according to reports.

**Pro-Active Engineering** added two **Mycronic** DX100 high-speed pick-and-place machines, with an expected capacity increase up to 40%.

**PVA** has expanded its service footprint in Mexico to include direct support in Monterrey, Chihuahua, Queretaro, and three field service engineers in Guadalajara.

Thermaltronics appointed Horizon Supply Group distributor.

**TopLine** has been granted US patent D908648 for a novel design for an adjustable fixture for aligning column grid array substrates.

**UTEP** researchers have developed a new low-cost Aerosol Jet Printing (AJP) system that's capable of fabricating hybrid electronic devices.

Valuetronics' new EMS factory in Vietnam will be fully operational in the third quarter.

Xiaomi will open two new mobile manufacturing plants and a television plant in India.

# PCB WEST 2021 Conference & Exhibition

Conference: October 5 – 8, 2021 Exhibition: Wednesday, October 6, 2021

SANTA CLARA CONVENTION CENTER, CA

# WHO'S EXHIBITING

Accurate Circuit Engineering Advanced Assembly AGC Nelco America Inc. All Flex Flexible Circuits & Heaters American Standard Circuits, Inc. APCT Arlon EMD Specialty Bay Area Circuits, Inc. **Bowman XRF** Cicor Group DownStream Technologies, Inc. DYCONEX AG Dynamic Electronics Co., Ltd. Elgris Technologies, Inc. Elsyca **EM Solutions Inc. EMA Design Automation Emerald EMS** Firan Technology Group - FTG Fischer Technology, Inc. Flexible Circuit Technologies **Fujipoly America** Goal Searchers Co., LTD Zhuhai GS Swiss PCB AG

GTS Flexible Materials Ltd. HSIO/Ironwood Imagineering, Inc. InnoLas Solutions GmbH IPC-2581 Consortium JetPCB USA Leader Tech, Inc. Mecadtron GmbH **MicroConnex** Minco Products, Inc. **MVINIX** Corporation Oak-Mitsui Technologies LLC Ohmega Technologies, Inc. Oki Printed Circuits Co., Ltd. **Optiprint AG** PCB Power **PFC Flexible Circuits Limited** Polar Instruments, Inc. Polyonics Printed Circuits Pulsonix PCB Design Software Quality Circuits, Inc. **Rogers** Corporation **Royal Circuits**

San Diego PCB Design San-ei Kagaku Co., Ltd. **Screaming Circuits** SEP Co., Ltd. Shenzhen Danyu Electronics Co. Ltd. Shin Yi PCB Co., Ltd. Siemens EDA Somacis Inc. Summit Interconnect Sunstone Circuits SVTronics, Inc. Taiyo America Inc. **Ticer Technologies** Trilogy-Net Inc. Ultra Librarian Varioprint AG Vayo Technology Ventec International Group Victory Giant Technology (Huizhou) Co., Ltd. Xiamen Bolion Tech. Co., Ltd. Zuken USA Inc.

# pcbwest.com

| STOCKED UP                                                                                                                                                        |      |               |      |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|------|

| Trends in the US electronics<br>equipment market (shipments only)                                                                                                 | NOV. | % CH/<br>DEC. |      | YTD% |

| Computers and electronics products                                                                                                                                | -1.5 | 0.8           | 1.0  | 9.2  |

| Computers                                                                                                                                                         | -0.5 | -2.4          | 5.3  | 4.5  |

| Storage devices                                                                                                                                                   | -1.8 | 1.4           | 20.4 | 30.7 |

| Other peripheral equipment                                                                                                                                        | 3.1  | -3.8          | 12.6 | 26.9 |

| Nondefense communications equipment                                                                                                                               | -7.4 | 2.8           | -5.3 | 15.3 |

| Defense communications equipment                                                                                                                                  | 8.7  | -11.3         | 3.7  | 8.4  |

| A/V equipment                                                                                                                                                     | -3.8 | -12.9         | 16.7 | 24.0 |

| Components <sup>1</sup>                                                                                                                                           | 0.7  | -0.5          | 1.3  | 8.1  |

| Nondefense search and navigation equipment                                                                                                                        | -1.2 | -1.0          | 2.4  | -1.4 |

| Defense search and navigation equipment                                                                                                                           | -2.2 | 0.9           | 4.8  | 6.7  |

| Medical, measurement and control                                                                                                                                  | -0.5 | 1.5           | 1.7  | 10.4 |

| <sup>r</sup> Revised. *Preliminary. <sup>1</sup> Includes semiconductors. Seasonally adjusted.<br>Source: U.S. Department of Commerce Census Bureau, Mar. 4, 2021 |      |               |      |      |

| US MANUFACTURING                                     | INDICES |      |      |      |      |  |

|------------------------------------------------------|---------|------|------|------|------|--|

|                                                      | OCT.    | NOV. | DEC. | JAN. | FEB. |  |

| PMI                                                  | 59.3    | 57.5 | 60.5 | 58.7 | 60.8 |  |

| New orders                                           | 67.9    | 65.1 | 67.5 | 61.1 | 64.8 |  |

| Production                                           | 63.0    | 60.8 | 64.7 | 60.7 | 63.2 |  |

| Inventories                                          | 51.9    | 51.2 | 51.0 | 50.8 | 49.7 |  |

| Customer inventories                                 | 36.7    | 36.3 | 37.9 | 33.1 | 32.5 |  |

| Backlogs                                             | 55.7    | 56.9 | 59.1 | 59.7 | 64.0 |  |

| Source: Institute for Supply Managemen, Mar. 1, 2021 |         |      |      |      |      |  |

| Source: Institute for Supp | oly Managemen, Mar. 1, 2021 |

|----------------------------|-----------------------------|

|----------------------------|-----------------------------|

| KEY COMPONENTS                                                                                                                                                 |       |              |       |                    |                    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------|--------------------|--------------------|--|

|                                                                                                                                                                | SEP.  | <b>OCT</b> . | NOV.  | DEC.               | JAN.               |  |

| Semiconductor equipment billings <sup>1</sup>                                                                                                                  | 40%   | 27.3%        | 23.1% | 7.6% <sup>r</sup>  | <b>29.9%</b> r     |  |

| Semiconductors <sup>2</sup>                                                                                                                                    | 5.79% | 5.86%        | 8.4%  | 9.55% <sup>r</sup> | 13.2% <sup>r</sup> |  |

| PCBs <sup>3</sup> (North America)                                                                                                                              | 0.93  | 0.97         | 1.05  | 1.10               | 1.14               |  |

| Computers/electronic products <sup>4</sup>                                                                                                                     | 5.15  | 5.01         | 5.13  | 5.11 <sup>r</sup>  | 5.06 <sup>p</sup>  |  |

| Sources: 1SEMI, <sup>2</sup> SIA (3-month moving average growth), <sup>3</sup> IPC, <sup>4</sup> Census Bureau, <sup>p</sup> preliminary, <sup>r</sup> revised |       |              |       |                    |                    |  |

# Hot Takes

- Total North American electronics manufacturing shipments rose 9.7% in January from a year ago. Sequentially, shipments fell 6.4%. (IPC)

- **Employment in US engineering occupations** is projected to grow 3% from 2019 to 2029, about as fast as the average for all occupations, with about 74,800 new jobs projected to be added. (Bureau of Labor Statistics)

- Global smartphone sales to end-users declined 5.4% in the fourth quarter, while smartphone sales declined 12.5% in 2020. (Gartner)

- The EMS sector recorded 26 transactions in 2020, down from 29 in 2019. (Lincoln International)

- The 2020 output of the cross-strait Taiwanese PCB industry increased 5% year-over-year to NT\$696 billion (US\$25 billion). (TPCA)

- Some 199 separate legal entities of 151 different EMS com-

panies in Europe had total revenues of €8.2 billion (US\$9.9 billion) in 2020, down 5.4%. (in4ma)

- Worldwide government IT spending is forecast to total \$483 billion in 2021, an increase of 5% from 2020. (Gartner)

- PC shipment volumes grew 12.9% in 2020. (IDC)

- Smartphone shipments are forecast to grow 14% year-overyear in the first quarter and 5.5% for the full year 2021. (IDC)

- Automotive electronics sales are predicted to hit \$641 billion by 2030, a CAGR of 7.6%. (Precedence Research)

- MOSFET chip prices are set to rise significantly in the months ahead thanks to worsening shortages arising from persistently tight 8-inch foundry capacity. (DigiTimes)

- Worldwide server shipments declined 3% year-over-year to nearly 3.3 million units in the fourth quarter. (IDC)

- Global DRAM revenue reached \$17.7 billion in the fourth quarter, a 1.1% increase from the previous year. (TrendForce)

- IC Insights raised its 2021 IC market growth outlook 700 basis points to 19%.

# **May 19, 2021** 1:00 pm – 3:00 pm EST

# How to Save Up to 25% on Your PCB Purchases

# Greg Papandrew \$75

Limited seating, register today! pcb2day.com

Professional Development Certificate included!

# Where Does Plug-and-Play Fit into Industry 4.0?

Communications interfaces rely on handshakes, but software and simplicity no longer go hand-in-hand.

"PLUG-AND-PLAY" seems a simple, efficient concept, a beautiful merger of elegant design and high technology. What happened to it?

I forget exactly when I first heard the term plugand-play, but it was sometime back in the late 1980s. As I recall, consumer electronics had something to do with it – perhaps a VCR player that connected to a TV. Or possibly it was tied to early personal computers, where the various accessories could be mixed and matched, so any brand of monitor, printer or keyboard could be added interchangeably to the system. Wherever the phrase came from, the meaning was universal: You could replace one part of a system with a new or different component, and the system would operate without a hitch.

In business the term seemed to morph in two directions. In administrative office environments, the term was associated with updates or upgrades to software. Transitioning spreadsheet software such as Lotus 1-2-3 to, say, Quattro Pro was seamless, thanks to the elegant design of similar operating commands. Just upload the new software onto your computer and begin using it. Meanwhile, on the manufacturing floor, a new piece of capital equipment could be dropped into the process flow and hooked up, and it fit seamlessly with the existing machines. *Voila!* New replaced old. Simple, easy, painless.

Regrettably, over time what was once plug-andplay has become complicated. Too often, when a "new and improved" version is introduced, the product interface also changes, not necessarily to improve the connection, but most certainly to appear new. As software and sensors replace traditional electromechanical options on newer, advanced manufacturing equipment, so too have most time-tested, mundane types of process equipment taken on entirely new looks.

Over the past decade, I have invested in a variety of capital equipment. Some is new technology, which understandably brings a steep learning curve as operators learn from scratch how it works, how it relates to processes up- and downstream, and all the collateral ways other processes may require rethinking and tweaking to best deliver the results the new process promises. I have also invested a significant amount in traditional processes, run on venerable equipment whose design has not changed for decades. When you duplicate or replace such equipment, most assuredly you think it will be a simple plug-and-play exchange or addition. Then reality sets in. The new and improved piece of equipment does not look or operate the same, and requires a total reeducation by all involved just to build product no different or better than has been produced for years. That's when I ask myself, "What happened to the simplicity of plug-and-play?"

If Industry 4.0 is the totally connected office and shop floor of the future, where sensors, computer power and feedback loops enable data to ensure quality flow, and if the traditional plug-and-play order (also known as Industry 3.0) is a shop floor of equipment performing binary tasks and equipment and processes operating virtually independently from each other, we may be living in an industrial *Twilight Zone!*

The sensors and interactive computing power required to enable equipment made by a variety of different companies performing different tasks to accomplish varying final results require elegant, high technology design to have the ability to communicate simply, flawlessly and continuously. And that is where *The Twilight Zone* comes in.

Quattro Pro's elegant design mimicked the operating communication commands of Lotus 1-2-3, enabling an easy shift between the software packages. The issue of intellectual property arose, however, with Lotus suing Quattro over patent infringements. The result: Quattro Pro had to remove that user-friendly, elegant design. Ever since, software companies have worked to differentiate product from competitors, and successfully made their "new and improved" version look totally different from the version it was replacing, to make it harder for competitors to copy, mimic or imitate their proprietary IP. IP protection certainly makes sense, yet it throws a wrench in the idea of achieving Industry 4.0's plug-and-play approach.

For the truly interactive shop floor, all the various manufacturers of capital equipment supplying industry – not just our industry – must be able to interface and interact with each other's equipment. More important, they need to be able to do it over generations of equipment, since the reality of manufacturing is equipment of all ages and origins is used. A new state-of-the-art machine has a better than 50-50 chance of being placed in service next to a 10-year-old model. Software suppliers have their work cut out for them. Not only must the operating system communicate universally, it needs to be upgradable and supported for decades!

Until that time, I fear we are living in industrial surreality, left wishing for plug-and-play simplicity, while struggling to try to best harness equipment to interact, leveraging all the necessary workarounds to make that myriad combination of exotic and mundane equipment that produces cutting-edge product work effectively together.

PETER BIGELOW is president and CEO of IMI Inc.; pbigelow@imipcb. com. His column appears monthly.

SPONSORED BYPCB2DAYSolder<br/>SolutionsSolutionsApril 14, 2021<br/>1:00 pm - 4:00 pm ET

# Tuning Up Your Stencil Printing Process

# Chrys Shea \$95

Limited seating, register today!

pcb2day.com

Professional Development Certificate included!

# 2021: A Year the EMS Industry Needs

It's a drink from an educational firehose, but the lessons will pay off.

MANY WILL DISAGREE with this column's title this month, especially supply-chain professionals working 24/7 to address a market with varying material constraints, continual logistics challenges and unforecasted demand spikes. That said, over the past few years the electronics manufacturing (EMS) industry has had a changing of the guard. While some replacements are veterans of the last round of market constraints, most haven't seen the perfect storm that 2021 represents. The lessons learned this year will create invaluable experience for this next generation of leadership. Here are a few examples:

Information technology. Over the past decade, even small EMS companies have upgraded their IT capabili-

time visibility into most of their critical metrics. However, while an exceptionbased real-time system is wonderful in situations where hapexceptions pen in relatively low volumes, it creinformation ates overload when it is identifying hundreds of exceptions in a month. The current market challenges are driving management teams to analyze what data they need to prioritize and how that data can be best formatted to help them stay

ties to provide real-

**SUSAN MUCHA** is

president of Powell-

Mucha Consulting

muchaconsulting.

com), a consulting

strategic planning,

training and market

positioning support

to FMS companies

and author of Find

It. Book It. Grow It.

A Robust Process for

Account Acauisition

in Flectronics

Manufacturing

smucha@powell-

muchaconsulting.

Services:

com

firm providing

Inc. (powell-

STOCK QUANTITY Reorder Point Safety Stock

ahead of shortages or capacity constraints. This will broaden the use of time-saving apps and create management teams with a better understanding of systems strategy strengths and weaknesses.

Supply-chain management. This year will likely teach newer supply-chain professionals a degree's worth of knowledge. Current constraints are driving a much more hands-on, collaborative approach to addressing critical material shortages. Risk management and negotiation lessons are being learned as companies decide how far beyond traditional forecast

windows to place orders and work with customers to negotiate better priority for essential products at the manufacturer. There will also be lessons learned in the use of non-franchised sources for scarce material and a better understanding of best practices in vetting these sources and documenting their use with customers.

Program management. Program managers are learning a wealth of lessons in terms of forecasting, capacity planning and working with customers in a materials environment with lengthening lead-times and increasing prices. This year will likely improve negotiation skills and risk management. And just as the telecom bubble in the '90s taught a generation of program managers to carefully document customer commitments on

continually increas-

ing upside orders, I

suspect this pent-up

demand bubble may also teach a few les-

sons when it eventu-

Inventory manage-

ment. The current

ics make it easy to

segue from a Lean

"pull" system men-

tality back to the old

"push" mentality

on the production

floor. If customer

orders are increasing

astronomically week

over week, doesn't it

make sense to build

out the products

with available mate-

dynam-

ally bursts.

market

INVENTORY CONTROL TIME ead Time

FIGURE 1. Material constraints mean supply-chain professionals must take a more hands-on, collaborative approach.

rial and production capacity earlier than scheduled so capacity will be available for next week's surprise upside demand? The answer is likely "yes" in an environment with continuing upside demand increases, assuming material can also be pulled in. A key lesson will be judging when demand is tapering and adjusting finished goods inventory accordingly.

Logistics. Transportation has been a wild card through most of the pandemic and will likely get worse before it gets better. A lot of air freight is transported on passenger planes, yet the number of flights has been reduced as discretionary travel slackened. Shipping and truck freight are over capacity. Cross-border shipments may be delayed by changing Covid-19 conditions that trigger changes in restrictions. In short, what used to be the simplest part of the manufacturing realization process now requires much greater coordination. That in turn is teaching multiple levels of EMS organizations about logistics options.

#### Continuity planning. Changing Covid-19 restrictions, par-

ticularly outside the US, are continuing to impact EMS facility operational status during a time when many facilities are at or near capacity. This is an acid test of the ability of impacted companies to transfer work among facilities. Longer term, this creates nimbler operational strategies and realistic planning that can efficiently support *force majeure* or disaster recovery activities.

Sales training. The most effective EMS salespeople are those who understand how their company addresses common challenges. This year will give every EMS sales team a full library of challenges and solutions stories, and likely a better understanding of key systems and processes associated with those solutions. At the same time, it will also open the door to more candid conversations with prospective customers. In a stable market, OEM sourcing teams often are reluctant to share information. In the current market, these same teams will spend more time in conversations evaluating prospective EMS suppliers' systems and processes for dealing with material constraints and upside demand. This will enable salespeople to build stronger initial relationships.

**Customer expectations.** The same changing of the guard found in EMS is taking place at OEMs. Challenges seen this year will teach the next generation of sourcing managers what their EMS providers can and cannot control. If there is a benefit to the pandemic, it is shared challenges have built more collaborative relationships among many OEMs and EMS providers.

OEMs will be well-served by a generation of sourcing managers who understand the benefits of that level of collaboration and the value EMS providers bring to this type of challengerich environment.

In a nutshell, as operationally difficult as 2021 is shaping up to be, the lessons conveyed this year will likely create a cadre of seasoned manufacturing professionals that will benefit the EMS industry and its customers for years to come.

venteclaminates.com

# The Art of Stifling Interference on a Printed Circuit Board Assembly

A printed circuit is an antenna for transmitting and receiving energy.

A RAGING FRATERNITY party with thumping house music can be annoying as the morning hours approach. Noise suppression ordinances to the rescue! The partiers have two choices: quiet down or get shut down.

In that sense, the fraternity party is like building an electronic circuit. If our machines make too much "noise" in any part of the spectrum, it's game over.

Just like kids can stop trampling everyone's lawn and come inside, shut the doors, windows, shutters and even the fireplace flue, we can also contain unwanted spectral emissions. Left unchecked, a printed circuit is an antenna for transmitting and receiving energy from within and outside the board.

Even a well-designed PCB has compromises. Our goal is to be ready to react to spurious emissions that take us beyond the allowable threshold. We start with a power budget, and a noise floor, and our electronics must comply with those design criteria while meeting regulatory requirements.

As we bring different functions aboard, the problems in the near field multiply. We think of high-speed transmission lines as the focus of our EMI abatement efforts. They are seen as the cause of the problem, owing to their signal rise times or a harmonic of that momentary event.

When the root cause is identified, the solution often comes in the form of an additional filter of some kind. Sometimes, that's not enough, and a more extensive re-spin of the board is needed. Just as good fences make good neighbors, so does metallic shielding around various circuits on the PCB.

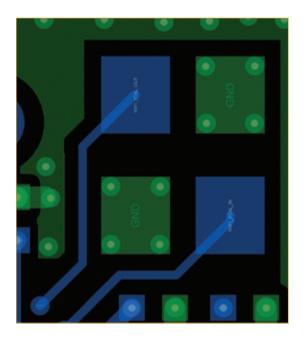

Coupling: That trace right there is really noisy. Pass it on! If nothing else, a frame around a circuit helps define

it as a group. Set off by the shield footprint, the part is already on its way to a happy state of affairs. The shield footprint is typically secured to inner ground planes by a ring of vias along the perimeter. That's all part of the 3-D Faraday cage that suppresses crosstalk within the board itself.

JOHN BURKHERT JR. is a career PCB designer experienced in military, telecom, consumer hardware and, lately, the automotive industry. Originally, he was an RF specialist but is compelled to flip the bit now and then to fill the need for highspeed digital design. He enjoys playing bass and racing bikes when he's not writing about or performing PCB layout. His column is produced by Cadence Design Systems and runs monthly.

Coupling is a nonlinear thing. The amount of coupling one element will receive from another is a function of the length and width of the gap between the two elements, as well as the magnitude and frequency of the signals. With all that factored in, doubling the gap will square the amount of isolation. That's a bargain, but it works both ways, of course. Cut the gap in half and the coupling is squared. Yikes!

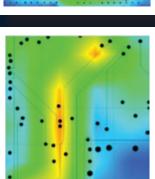

An interactive heatmap to show us the price of rotating an inductor or adding an extra decoupling cap would be nice. Right now, that is an outside function known as SI/PI. Signal integrity/power integrity is the branch of engineering that simulates circuits and saves us from critical mistakes. As the PCB becomes more advanced, SI/PI simulations become much more important.

**Coexistence:** Making each constituent equally uncomfortable. The only way to get space for something is to take it from something else. This fact of nature is in play for most power distribution networks. We often have just enough copper to meet the overall

FIGURE 1. More participants mean more noise.

**FIGURE 2.** Generational shrinkage of a WiFi radio over the product lifecycle. They are much smaller these days.

#### power requirements and then only if it is apportioned exactly (FIGURE 2).

Getting the balance right is most important when power is limited. Mobile consumer electronics walk a tightrope of high performance with low power consumption. Inevitably, the battery grows to crowd the electronics together. When it comes to the final form factor, the shields will cover nearly all the components as a substitute for the space they had on the breadboard.

After all circuits are fully integrated and playing nice together, it's time to consider the world of other devices. Bottling up EMI is helped by the metal enclosures, plus an awareness of the noise sources and the circuit elements most affected by noise.

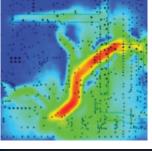

Aggressors: The party animals of the electronics world. We can depend on some circuits to be a house party. One of the characteristics of a noisy circuit element is that they never have a rest state. A crystal will hum along nonstop. A switch mode power supply turns on and off at a certain rate by design. These two players are not usually switching their states all that fast. It's those harmonics that come into play. Clock traces do the same thing and may not need the help from harmonics, but they get it.

The strategy here is to create a jail that keeps the spurious signals bottled up. For crystals, I like to isolate them with a moat in the copper pour that helps contain their emissions (FIGURE 3). Not only is the copper pulled well back, no ground vias are nearby to introduce the crystal to the inner planes.

**FIGURE 3.** Isolating a crystal's ground pins from the surrounding copper pour. (I rotated the circuit along with the route-keep-out after this screen grab.)

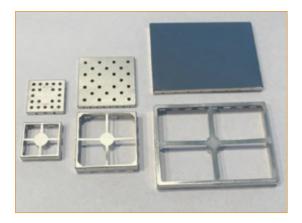

**FIGURE 4.** Off-the-shelf shielding solutions with precut "mouse holes." The crossmembers stiffen the shield walls and provide a central pickup location for automated assembly. The lids can be perforated for airflow. (Source: Laird)

Layout of a switch mode power supply (SMPS) will feature an inductor on the output pin. The shape that connects the output pin(s) to the inductor is the power supply's megaphone. That connection must be short and only wide enough for full power transfer. Aim for a rectangular placement of each power supply sub-section. Voltage conditioning can go near the main supply, but individual power supplies should be located nearer their respective loads.

The repeated focus on clean power is because a good power distribution network will help cover for some shenanigans on the routing portion of the board. It's just a fact that some chips require a few compromises to get through the fan-out.

Victims: Some circuits are designed to listen, and that's what they do. If you are already fighting EMI/EMC issues, it pays to take a good hard look at the power distribution, as well as the grounding scheme. Sensors and other similar devices are effective at picking up unwanted interference. In their case, the shield isn't so much a jail as it is a penthouse where the listening device of whatever type can do its thing in peace.

Receiver circuits are more susceptible than the transmitter side. The higher magnitude of the TX signal raises the noise floor. Most of the traces on a board can be classified as one or the other, with I/O lines being a little of both. Locate the sensitive receive circuits as far as practical from the noisy inductors and other culprits. An elegant layout has these attributes and provisions to increase isolation, should the need arise.

The most common shielding type is the two-piece type that has walls and a lid that presses on over the walls (**FIGURE 4**). This allows field service once the shield is installed, while the single-piece shield must be unsoldered from the board for work under the hood. Another way to use a single piece shield is to solder down little clips that hold the shield in place. Is that still a one-piece shield? The companies that make those also make a few standard-size covers to plug and play.

Of course, a two-piece will cost a little more. A four-sided shield with 90° bends keeps costs down. A six-sided L-shape or chamfered edge is not so bad, but costs will rise for polygonal versions. Multiple pockets within a single shield are possible. These are popular with analog circuits where multiple radios are in use.

Materials are generally stainless steel, with aluminum or nickel-

continued on pg. 32

# Easy PCB PCB PROTOTYPING MADE EASY EASY QUOTE/INSTANT PRICE

The **ORIGINAL** Conference and Exhibition for Printed Circuit Board Design, Fabrication and Assembly on the **EAST COAST**.

# **NEW DATES:**

Conference: June 15 - 17 Exhibition: Wednesday, June 16

Best Western Royal Plaza Hotel & Trade Center Marlborough, MA

# WHO'S ON BOARD?

The **ORIGINAL** Conference and Exhibition for Printed Circuit Board Design, Fabrication and Assembly on the **EAST COAST**.

- Lee Ritchey

- Rick Hartley

- All-new workshops on PCB Design for Optimum Fabrication and Assembly and A Comprehensive Guide to PCB Design Necessities

- More than 50 hours of training

- Professional certificates of completion

- Special free session: The Most Common Design Errors Caught by Fabrication

# DC Analysis: Keeping PDN Running Smoothly (Not So Easy Anymore)

Many new products need tighter hardware.

TWO COMPELLING FORCES driving much of our technology - miniaturization and performance - are not new. In fact, one could say they have appeared within every product spec and design document in some form or another since the terms were coined. Fundamentally, this has enabled capability and portability with products in virtually every hardware sector. This will (and should) continue. In the area of miniaturization, both board and package are transforming as technologies such as rigid-flex, blind/buried vias, and multi-die packages move from fringe to mainstream. Further, performance improvements maintain the well-known doubling trajectory and are propelled forward by orders of magnitude in speed, while increasing efficiency and extending battery life. Often these gains are continually achievable only by reducing the voltage swing to under a volt. As miniaturization and performance drive devices to new functionalities and applications, the effects of these requirements are visible throughout the design process. Nowhere is this drive for smaller, faster, cheaper more noticeable than in power.

TERRY JERNBERG is an applications engineer with EMA Design Automation (emaeda.com), with a focus on PCB design and simulation. He spent his early career on signal integrity simulation for the defense industry and was fundamental in the adoption of these tools at EMC and Bose. A vocal advocate for simulation, his enthusiasm for physical modeling has expanded to include power and thermal capabilities

Power demands outpacing supply. To comprehend the extent of the power delivery network (PDN) transformation, consider the following. Design requirements associated with power delivery have become substantially more complex, with many ICs requiring power to be supplied at multiple voltage levels. Frequently those levels are near or below a single volt, contracting virtually every threshold and reducing margins to mere millivolts. Simultaneously, demand for current has skyrocketed in some product areas, made obvious by the extent to which we now account for adequate cooling. In addition to these increased electrical demands, the PDN must also be more responsive, capable of supplying the instantaneous current demands of high-

speed signaling. While all this may suggest a more robust PDN is needed, as many new products reach manufacturing, often the opposite is true. Not surprisingly, the miniaturization effort has had a consolidating effect on the physical hardware, frequently bringing high-current ICs closer together (FIGURE 1). Advances in device packaging have contributed as well. Pin counts can easily exceed a thousand on a single package, and mainstream spacing under a millimeter contributes to the same reality: The PDN is comprised of less copper in today's PCB than it was just a few years ago.

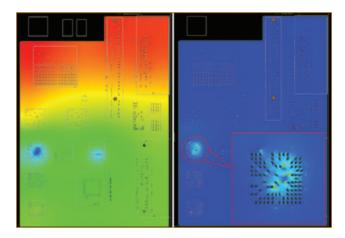

Controlling the PDN from the start. Recognizing this is a trajectory where power delivery will become problematic, and conceding that for some designs it already has, progressive product development teams are looking to power integrity simulation for answers. We'll see in subsequent columns several elaborate interactions attributable to the power system, such as complications with "the return path" and the ability to shield and control EMI, but first we need to ensure adequate capacity and effective distribution. Commonly referred to as the "DC" branch of power integrity, its primary task is to guarantee sufficient current sources at a steady voltage. The PDN must provide a conductive path such that current leaving the supply does not experience so much resistive loss the voltage can't be maintained when the device is drawing its maximum current. It is essentially an Ohm's law problem. By understanding a device's operating voltage and maximum current draw are defined by its specification, we quickly see PDN resistance is the only design element in which a product team has any control. Signal integrity has taught us the physics associated with current flow and electrical conduction are very predictable. We recall that with knowledge of the materials and conductor geometry, accurate/predictive characterization of electrical behavior can be determined. Mathematically, power integrity, aka PI or PDN simulation, has many similarities with its signal integrity roots. What is strikingly different, however, is the actual copper under examination and the current being conducted. Contrast the wide copperflooded areas (to include entire planes) associated with power routing with the thin line of a signal trace, and we'd naturally expect the resistance to current flow would be much different. Likewise, consider the short bursts of current we see when digital signals switch, first in one direction and then the other, and compare

FIGURE 1. Multiple power planes have become the norm.

those to the steady drain, source to load, we see for power signals. Therefore, the physics of conduction are the same, but the signals conducted are very different, requiring different types of analysis and methodologies to meet our power delivery goals and demands (FIGURE 2).

FIGURE 2. IR drop vs. current density.

DC aka distribution and capacity. As noted, our DC goals for power delivery, or PDN, can be broadly defined as distribution and capacity. Distribution implies all devices, even those farthest from the supply, have access to adequate current at the defined voltage. Similarly, under extreme demand, capacity ensures the power system can maintain that voltage, even when current draw reaches its allowable maximum. If the voltage supplied at every device doesn't droop below the acceptable value, we can have great confidence that even if each device needs to draw its most aggressive current, the power delivery network is capable of distributing adequate current to all devices.

Solving for V. The DC capability associated with power integrity simulation requires only two things: an accounting of load and resistance. An accounting of load is simply how many devices are being supplied and how much current each device requires. Cumulatively, this is the "I" in our Ohm's law (V = I x R) reference, while "R" is resistance. We know from previous discussion simulators routinely calculate resistance, even impedance ("complex resistance"), given only the materials and geometry contained in their CAD databases; this is exactly the case with power integrity. Often accessible directly from within the PCB CAD tools, PI simulators can readily identify conditions where a chip could become "power starved," but it doesn't stop there. Because the tools create a model of the board, all the properties (voltage, current and resistance) can be displayed as color-coded overlays directly on the board's etch. This enables both visualization of a problem and an environment where corrections can be made in the native CAD tool and be reflected in the design file. While not specifically addressing Power DC issues (one of distribution/capacity), these additional overlays are useful for identifying other concerns associated with power as well. Areas of high current

density, which could result in both EMI defects and reliability issues, can be easily detected and prevented, as the simulators produce an intuitive, visual model of the power network.

Moving up a level of abstraction. Power integrity DC simulators exist from a number of vendors and have universally proved accurate. This is largely due to the extensive studies on copper conduction for the RF and high-speed digital industries. While traditionally this type of analysis has been done at the layout and routing phase of the PCB, it is increasingly apparent analysis needs to move up a level of abstraction to incorporate earlier system-level, power budgeting and inspection (FIGURE 3). In this analysis, for example, a DC-to-DC convertor's dual role would be recognized, both as a load to the main supply net and the origin (supply) of the power net produced at its output. Leveraging the PCB model as a Spice model, external circuit elements such as switches, resistors and transistors can be included, permitting simulation of the system itself. Extending system-level checks to include device Spice models extends both the checking and display capability beyond individual nets to the system. This enables "sizing" and capacity checks to encompass device selection and verification, in addition to the checks performed on the etch alone.

PDN pressure is not going away. Although the technologies that will drive product direction in any hardware sector cannot be predicted, it's safe to say there is little desire for bigger, slower, less-efficient anything. Therefore, miniaturization and performance will continue to be prominent, and they have their sights on all that "extra power plane copper."

Will you be ready?

FIGURE 3. Power design is a hierarchical problem. Source: Sigrity Power Tree.

# lf you can see it, you can fix it

# A powerful way to look at your design

- · Rapidly diagnose and identify EMC/EMI challenges

- Real-time compact tabletop instrument

- Cost effective solution on your lab/test bench

- Up to 8.0 GHz

In co-operation with Trilogy-Net

# www.yictechnologies.com

Join us at Booth 34 Wednesday 16th June 2021, Marlborough, MA

support@yictechnologies.com

# High-Speed Telecom Requires 'Dialed-In' Materials

Stronger, faster and more robust networks will be one of the positive legacies of the pandemic.

HOPEFULLY, WE WILL soon be able to start living our post-Covid-19 lives. Going forward, some of us want fundamental changes. Others are keen to return to the way things were. Although we will be pleased to put this situation behind us, some things are here to stay. One, obviously, is the lethal group of coronaviruses that will surely continue to take lives after lockdown (we hope at a greatly reduced rate). Another, I believe, is the tendency for many of us to continue working from home (WFH) to a much greater extent than before.

WFH has been one of the headline trends of this crisis. Although clearly not to everyone's taste, it could turn into a revolution founded on the internet technologies that allow us to meet with colleagues online, access data and tools remotely, and benefit from high connection speeds wherever we are – wired or wireless. That so many can do meaningful work this way also reflects the soft nature of many tasks associated with getting things done in developed economies. These soft deliverables liberate us from location and will be critical to our economic survival of this pandemic.

Many are keen to recover the social dimension to our working lives. While physically working together in the same space and time to achieve shared goals is a powerful part of team building and cohesion, we can also take advantage of the flexibility to ease some of the more stressful aspects, such as traveling and being away from loved ones.

WFH has also powered a rise in IT equipment sales as lockdown periods have been enforced across the world. Internet use has surged 30% in the past months, challenging the networks to support this explosion of connectivity. In addition, service providers and end-users are more aware of security vulnerabilities and the importance of protecting people and assets against cyberattacks. As if securing connected devices within a restricted campus is not difficult enough, widespread WFH significantly extends the attack surface available to hackers.

ALUN MORGAN is technology ambassador at Ventec International Group (ventec-group. com); alun.morgan@ ventec-europe.com.

Among the techniques put forward to protect and manage telecom networks, AI is perhaps one of the most powerful and exciting. The ability to predict the usual and identify the unusual in its midst is the key to AI's power in these roles. By anticipating usage patterns, AI can help network operators provision resources optimally to ensure resilience and maintain uptime. At the same time, the technology has become sophisticated enough to distinguish the many small aberrations that characterize human behavior from the more seriously unusual events likely associated with fraudulent activity and cybercrime. Underlying everything, of course, are demands for greater speed and capacity driven by the uptick in reliance on the internet for work and social connections. This involves committing to rolling out the new generations of high-performance hardware needed to handle the extra subscribers, extra traffic density, and extra speeds. In the last telecom boom, just before the 2001 dotcom bust, I worked with leading hardware vendors involved in building incredibly large multilayer telecom switch backplanes, up to 60" x 48", with as many as 40 layers. Getting these boards to operate at the speeds required, while also achieving the thermal performance needed to ensure reliability, proved extremely challenging.

While the physics of the situation have not changed in the intervening years, the materials at our disposal have. So, too, has our understanding of the interdependencies among parameters like signal speed, trace dimensions, energy loss, and dielectric properties. Getting the best tradeoff is critical to meet the world's connectivity needs going forward.