The Annual PCD&F Design Engineer Salary Survey

PRINTED CIRCUIT f.com DESIGN&FAB

Materials Considerations for **ADAS Radars**

pcdandf.com

circuitsassembly.com JUNE 2020

H

Via Padstacks

The Myth of Current Density

> Radiation Overdose?

**Conference Catalog**

This issue of Printed Circuit Design & Fab/Circuits Assembly is brought to you by:

PCB WEST 2020 Conference & Exhibition

Conference: September 8 - 11 Exhibition: Wednesday, September 9

# See you in September!

Register Now

Conference Catalog Online \*More than 35 sessions, plus 11 free classes!

\*All the hot topics, including grounding, power distribution, signal integrity, flex circuits, and RF circuits

\*Training for designers, fabricators and assemblers, from novice to pro

\*Rick Hartley and Lee Ritchey

\*Professional Development Certificates

\*One-day FREE Expo with 100+ leading suppliers

# PCBWEST.COM

SANTA CLARA CONVENTION CENTER, CA

# **ON-DEMAND WEBINAR**

# It's All About the Space: A Tribute to Ralph Morrison

- Introduction by Daniel Beeker

Life, Education and Publications

Ralph's Rules

- 🔗 Field Stays Put

- Selectromagnetic Field Energy

- ⊘ The Rule of Triplets

- How a Signal Propagates on a Microstrip

PC Board Design for Low EMI: Rules

- ♂ Typical, But Poor, 4-Layer Design

- Contract Con

- C Lower EMI 6-Layer Board Stack-Up

- C Lower EMI 8-Layer Board Stack-Up

Ralph's Rules: Field Stays Put

Very POOR 8-Layer PC Board

SIERRA CIRCUITS

Very POOR 10-Layer PC Board

- Discontinuous Return Paths & Crossing Gaps

- 🧭 Demo-Gap in Return Plane

- Difference Between Gapped and Ungapped Traces

**Presented by:**

# SIERRA CIRCUITS

WEBINAR It's All About the Space

A tribute to

RALPH MORRISON

Presented by: Daniel Beeker, Rick Hartley, Kenneth Wyatt and Elizabeth Morrison

# WATCH NOW

https://pages.protoexpress.com/ralph-morrison-webinar.html

# The All New EDA Store

# Zero Impedance CAD Purchasing.

Visit the all-new EMA online storefront and shop our collection of CAD products anytime; day or night. Here you will find a broad array of products to help you design faster and more efficiently. Should you need it, our team of experts are here to help answer questions, provide demos, and support you through CAD tool selection.

Best of all, you can rest easy with our upfront, transparent, and hassle-free purchasing process.

Start Shopping Now

# NULLION DOLLAR PRODUCT GIVEAWAY

Celebrating 30 years of JTAG Boundary Scan

60

www.xjtag.com/giveaway

\*Terms and conditions apply.

TLB, a global leader in the 4th industrial revolution.

# **TRUST 2030**

Good Company in 20 Years, Great Company in 30 Years.

is specialized in manufacturing PCB for semiconductors. By joining World Class 300 in 2018, we have become a company specializing in materials and components leading the fourth industrial revolution. Based on technology and quality, we will establish ourselves as a material parts company that leads not only Korea PCB but also world PCB.

# DRAM Module / SSD Module

IOT / Build-up Board

Semiconductor TEST B'd & 5G Network System

15602) 305, Sinwon-ro, Danwon-gu, Ansan-si, Gyeonggi-do, Republic of Korea Tel.82-31-8040-2096 Fax. 82-31-492-6623 Domestic Tel. 82-31-8040-2071, E-Mail. cmh@tlbpcb.com Offshore Tel. 82-31-8040-2060, E-Mail. will\_shin@tlbpcb.com

RUSHPCB

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB ELECTRONIC DESIGN, & QUICK TURN CIRCUIT BOARDS, ASSEMBLY & FULL TURNKEY

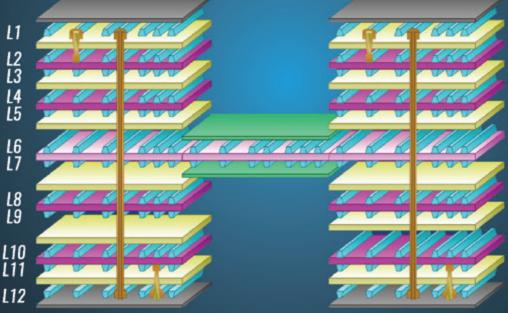

# Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

# When you're in a rush call RUSH PCB

Affordable Pricing • Satisfaction Guarantee • Fast Response • Free Quote • Fast Shipping HDI Boards • Stacked Micro Vias • 2 mil line & Space • Flex & Rigid Flex

# Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL

www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

## **FIRST PERSON**

#### CAVEAT LECTOR

Surface glances. **Mike Buetow**

## MONEY MATTERS

#### 12 ROI

Covid epiphanies. **Peter Bigelow**

## **13 FOCUS ON BUSINESS**

Viral marketing. Susan Mucha

### 15 BOARD BUYING

Your PCB supplier has been acquired. Time to run? **Greg Papandrew**

# TECH TALK

### **16 DESIGNER'S NOTEBOOK**

Breaking down via padstacks. **John Burkhert**

# 17 MATERIAL GAINS

Has the time come for performance-centric materials specifications? **Alun Morgan**

## **18 THE FLEXPERTS**

Uneven layer counts. Nick Koop

### **39 SCREEN PRINTING**

It starts with the foundation. **Clive Ashmore**

# 40 TECH TIPS

Bent out of shape. **Akber Roy**

# 41 DEFECT OF THE MONTH Pin-in-paste defects. **Bob Willis**

#### 42 TEST AND INSPECTION Radiation overdose? David Bernard, Ph.D.

# PRINTED CIRCUIT DESIGN & FAB

# FFATURES

#### 20 PCB LAYOUT

## Stop Thinking about Current Density and Via Temperature

Many designers and some EDA design tools place heavy emphasis on current density when sizing traces for a given current. But it is much more complicated. Following this design rule blindly may lead to significant design errors, especially when designing vias for allowable current. by DOUGLAS G. BROOKS, PH.D.

#### COMPENSATION 25

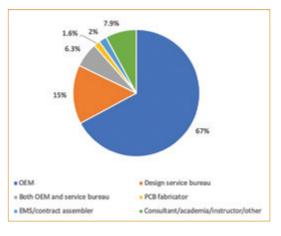

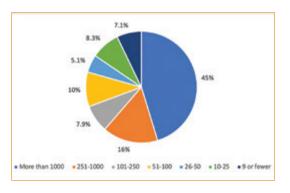

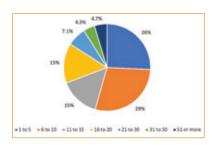

#### It Was Predicted for Years. Engineers Are Finally Taking Over PCB Design.

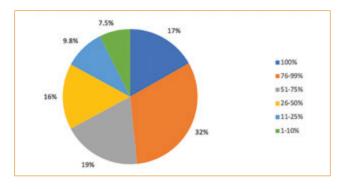

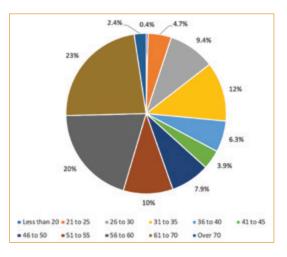

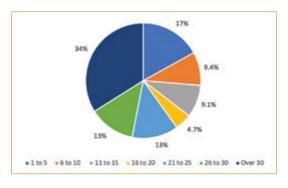

The annual PCD&F salary survey results suggest newcomers may be entering the field. by CHELSEY DRYSDALE

#### HIGH-REL ELECTRONICS *(cover story*) 28

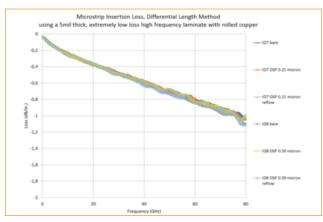

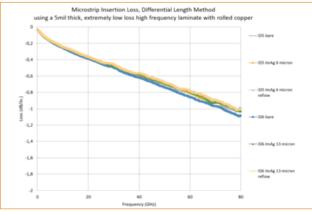

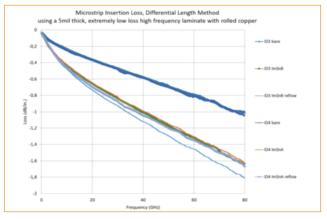

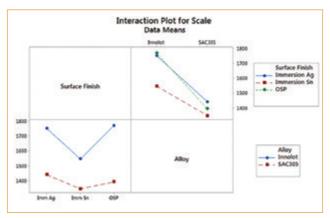

### Materials Considerations for Automotive Radar Designs

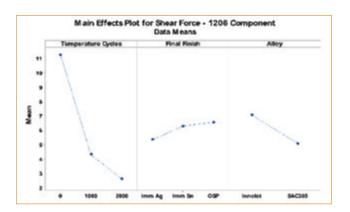

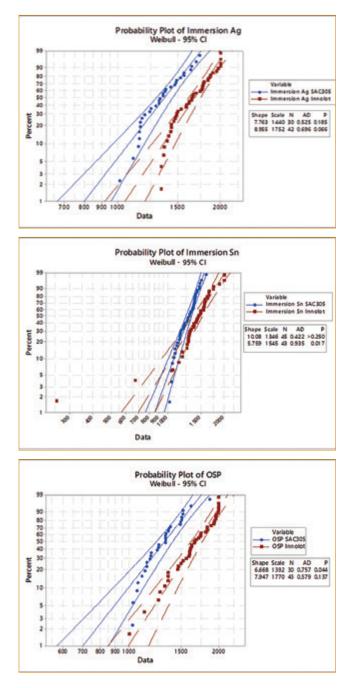

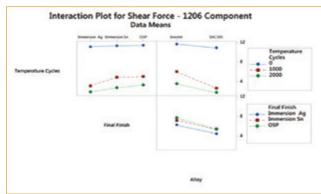

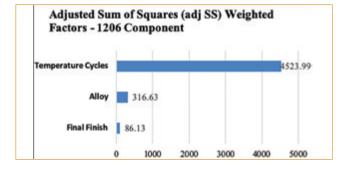

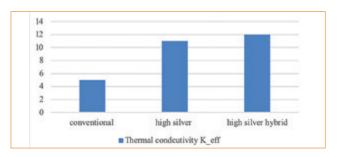

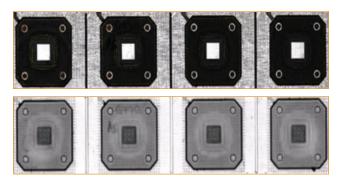

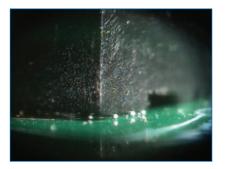

Advanced safety systems require cars to react in response to external changes, leaving decisions to the vehicle, not the human occupants. An investigation of chemical process changes needed to improve radar module reliability, looking at radar designs, reliability requirements, and improvement options at the board and packaging levels. by LENORA CLARK, PAUL SALERNO and SENTHIL KANAGAVEL

#### **INEMI ROADMAP** 37

#### **High-End Systems Products**

New high-end computing system technologies becoming available for such applications as servers, telecom and the cloud must meet bandwidth, power, thermal and environmental challenges. The packaging technologies - including SiP, MCP and DDR5 - that will be integrated into high-end computing systems will be those that are successfully developed with acceptable cost and risk of adoption. by KARTIK ANANTH and DALE BECKER

# IN THE DIGITAL EDITION

## The Digital Route

The latest happenings of the Printed Circuit Engineering Association. by KELLY DACK

# **DEPARTMENTS**

- **AROUND THE WORLD** 8

- **MARKET WATCH** 11

- **OFF THE SHELF** 45

- MARKETPLACE 47

# ON PCB CHAT (pcbchat.com)

Intervala's Acquisition Strategy with TERESA HUBER

PCB Cł

Machine Learning and AI in Electronics with SEBASTIAN SCHAAL

MES and AR in Assembly with DAVE TRAIL JR.

# INTRODUCING THE **YSP10** SOLDER PASTE PRINTER

- The industry's first solder paste printer that boasts a completely automatic changeover system

- Enabled by automatic support pin exchange, automatic stencil replacement, and automatic solder paste transfer functions

- The YSP10 can remove solder paste from an existing stencil and transfer it to another in about one minute with zero operator interaction

- Eliminates all operator involvement in the changeover process

- Reduces program changeover time from more than 15 minutes to a mere 2 minutes\*

# COMPREHENSIVE PCB DOCUMENTATION

Use 3D Models for Superior PCB Assembly Illustrations

Manage Layer Stackup Design and Materials

# BluePrint PCB

BluePrint automates the PCB documentation process, creating comprehensive electronic drawings to drive fabrication.

of imported CAD data as a 3D PCB

Lowers documentation cost and time

Increases documentation detail & accuracy

Shortens PCB design cycles

Reduces documentation time by 60-80%

# downstreamtech.com • (508) 970-0670

©2020 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

# PRINTED CIRCL **DESIGN** & FA pcdandf.com

circuitsassembly.com

# **EDITORIAL**

EDITOR IN CHIEF Mike Buetow 617-327-4702 | mbuetow@upmediagroup.com

SENIOR EDITOR Chelsey Drysdale 949-295-3109 | cdrysdale@upmediagroup.com

DESIGN TECHNICAL EDITOR Pete Waddell

EDITORIAL OFFICE P.O. Box 470, Canton, GA 30169 | 888-248-7020

#### PCD&F CONTRIBUTING EDITORS

Akber Roy, Peter Bigelow, John Burkhert, Mark Finstad, Bryan Germann, Bill Hargin, Nick Koop, Greg Papandrew

CIRCUITS ASSEMBLY CONTRIBUTING EDITORS AND ADVISORS Clive Ashmore, David Bernard, Robert Boguski, John D. Borneman, Joseph Fama, Susan Mucha, Chrys Shea, Jan Vardaman, Ranko Vujosevic

# PRODUCTION

ART DIRECTOR AND PRODUCTION blueprint4MARKETING, Inc. | production@upmediagroup.com

# **SALES**

SALES DIRECTOR Frances Stewart 678-817-1286 | fstewart@upmediagroup.com

SENIOR SALES ASSOCIATE Brooke Anglin 404-316-9018 | banglin@upmediagroup.com EXHIBIT SALES

Frances Stewart 678-817-1286 | fstewart@upmediagroup.com PRINT/FLECTRONIC REPRINTS

cdrysdale@upmediagroup.com

# SUBSCRIPTIONS

For changes, additions or cancelations: subscriptions@upmediagroup.com

# **UP MEDIA GROUP, INC.**

PRESIDENT Pete Waddell

VICE PRESIDENT. SALES AND MARKETING Frances Stewart

VICE PRESIDENT. EDITORIAL AND PRODUCTION Mike Buetov

DIRECTOR OF GROUP SHOWS

Alyson Corey acorey@upmediagroup.com

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. For others, annual Subscription Rates in U.S. funds are: \$80 (U.S. and Canada), \$145 (all other countries). Single copy price is \$8.50. All subscription and single copy orders or inquiries should be directed to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169, email subscriptions@upmediagroup.com. Photocopies and issues on Microfilm/Microfiche (16mm, 33mm or 105mm) are available from University Microfilms International, 300 N. Zeeb Rd., Ann Arbor, MI 48106, Telephone 313-761-4600.

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by UP Media Group Inc., PO Box 470 Canton, GA 30169. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

Periodicals postage paid at Canton/Ball Ground, GA, and additional mailing offices. © 2020, UP Media Group, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/CIRCUITS Assembly is forbidden without written permission.

Postmaster: Send address changes to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169.

# From wafers to packaging to everything in between...

The microelectronics industry counts on SEMI standards to drive innovation in every aspect of product design and manufacturing.

Explore the wide variety of SEMI standards and get involved in setting standards for your segment with our open, consensus-based process.

Learn more and get involved at:

# semi.org/standards

# CAVEAT LECTOR

MIKF BUETOW EDITOR-IN-CHIEF

# The Virtual Tour

E'VE SPOKEN AT length in these pages about the virtual factory. But what about the virtual factory tour?

By this, I don't mean the flashy, MTV-style videos found on so many company websites today. Instead, a live plant tour, executed using cameras and PCs.

I have been studying manufacturers to determine whether, in the wake of the coronavirus surge, they are noticing changes in the way customers decide where to put production, and whether that's a permanent change or a temporary fix. According to my unscientific sample, the answers are "yes" and "we're not sure."

Count Teresa Huber, president and chief executive of Intervala, among those seeing changes. The EMS company, which has sites in Pennsylvania and New Hampshire, is substituting video conferencing for onsite meetings and in-person audits.

"We are seeing more video conferencing, and we have processes in place to share documentation on processes, give quality yield data from internal production, interface electronically," she told me. "We are definitely seeing a trend in that being the way things get done. People are getting more comfortable with the idea they may not be able to physically touch where their product is going to be made. We can reassure them through a combination of data, online conferencing, and a lot of customer references."

On SMTC's quarterly conference call, chief executive Eddie Smith said restrictions on travel and factory visits are turning tablets into voyeurs. "We can't allow people in our factories, and so the question becomes can we virtually get approvals from our customers using GoPros and iPads, in terms of the manufacturing process?"

Just prior to the Covid-19 pandemic, Joe Fama, a longtime EMS business development exec who focuses on Southeast Asia, had the same thought, albeit for different reasons. He implemented live virtual tours at a plant he worked with in Vietnam, surmising it could be a substitute for expensive and time-consuming travel.

Fama's tours run the entire factory, from the front door to the production floor. Using FaceTime broadcast via an iPad, the "escort" walks the customer through SMT, clean rooms, inventory, testing, and shipping.

According to Fama, the customers drive the process, much like an actual plant tour. "We ask them, 'Who do you want to see? What do you want to ask them?" he told me. "The customer plans out what they want to see. We tried to get a candid, unabridged response from the line workers, and if they want, they can meet with the C-level executives and engineering too."

For those considering similar arrangements, he offers these suggestions: "To prepare, make sure the right people are available. From a housekeeping perspective, have the plant in reasonable order, with no debris or confidential materials in the line of site."

Fama draws a distinction between an in-plant visit and its virtual cousin. The in-person audit is more formal, he says, with much more introductions. Virtual, he adds, "is more like an unrehearsed, spur-of-themoment walkthrough."

"It's an all-day process," he says, but it works well. He says they landed all four prospects that went on the virtual tours yet had not visited the plant in person. One went right into tooling just after the virtual tour, he added.

It remains to be seen whether the changes will be longer term or whether we will go back to normal, whatever normal may be, at some point. "We've all had to adapt and rethink and figure out creative ways to get things done in a very different way," Huber notes.

"Customers who are auditing and making decisions are much more comfortable if they can walk in a factory and talk to people and see it, feel it.

Another multinational EMS with plants in the US and Mexico I spoke with said some customers are deciding to source sight-unseen. They added that others he spoke with said they could see the value of a virtual tour, but if the product is really complex, they probably want to see who they are sourcing it to.

Because the line layout tends to be linear and the factories open, assembly lends itself to virtual tours. Board fabricators might be more complex, especially in the West, where job shops prevail. Still, the fabricators I spoke with felt the concept had some merit.

The overwhelming sense I get is backlogs are firm and business is continuing despite the pandemic. If going virtual can keep the sales process running smoothly, manufacturers should consider it.

mbuetow@upmediagroup.com

@mikebuetow

P.S. The show must go on! Check out the PCB West show catalog at pcbwest.com or in the digital version of this issue.

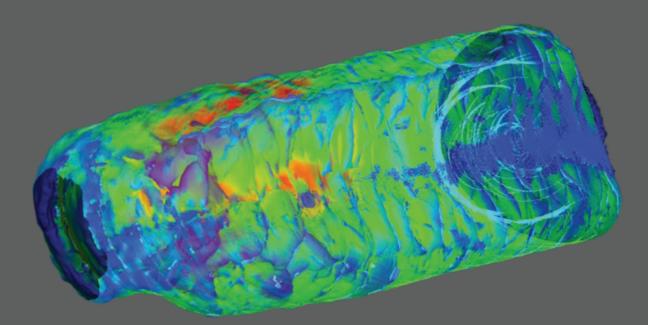

# **Datest's Imaging Technology** Illuminates Fossils.

# This is a fossil.

The colors correspond to thickness.

After 2 million years, technology tells a colorful tale.

Why does that matter?

Because CT scanning provides meaningful interpretive data for lots of objects.

To help scientists understand the work of millennia, and help engineers solve problems.

Test Engineering. Failure Analysis. Answers.

47810 Westinghouse Drive • Fremont, CA 94539 Phone: 510-490-4600 • Fax: 510-490-4111 Email: Info@datest.com • Website: www.datest.com

## **PCDF** People

Collins Aerospace named **Jennifer Was**kow director of engineering systems.

Karl Dietz, a PCB materials expert who spent more than 40 years at DuPont Electronics Materials, passed on May 5.

Galaxy Circuits named **Carl Schlemmer** director.

Google awarded a \$43,000 grant to a professor of electrical engineering at Missouri University of Science and Technology who is using machine learning to bridge the gap between PCB design theory and the requirements of more complex electronics.

Innovative Circuits promoted **Chris La Croix** to plant manager.

Murrietta Circuits appointed Kevin McCartney business development manager.

TE Connectivity named **Martin Bayes** fellow – corporate technology.

Ventec announced **Thomas Brämer** has joined the company as technical sales representative for Germany. He has over 30 years' technical and sales experience in PCBs

with Vaas Leiterplattentechnologie, Kubatronik, CCI Eurolam, and others.

# **PCDF Briefs**

Apex International will purchase a PCB plant in Thailand in 2020, which will boost the firm's monthly production capacity 20% to 600,000 sq. m.

Apple is contemplating use of in-house chips for one or more of its Mac computers, moving away from its longtime supplier **Intel**.

Averatek named RBP Chemical Technology distribution partner.

**Caiz Optronics** named **ATIF Holdings** business advisor in anticipation of its entrance into the US fabrication market.

**EMA Design Automation** has partnered with **Dassault Systèmes**.

**EnviroLeach** is gearing up to bring its Canadian circuit board recycling facility to commercial-scale capacity in the next two months.

FH Bielefeld University of Applied Sciences purchased a Nano Dimension DragonFly Lights-Out Digital Manufacturing system.

Freedom CAD Services named Tech Generators representative.

# 'The Workbench of the Future': InspectAR Aims to Disrupt Debugging Process

**ST. JOHN'S, NEWFOUNDLAND** – Newfoundland may not appear to be a hotbed for PCB technology, but a team of startup engineers may change that. There, on the Eastern edge of Canada, Liam Cadigan and Darryl Day, who grew up together, were working on degrees at Memorial University, where they met fellow engineering student Matt Noseworthy and budding computer scientist Nick Warren.

The group applied for the SpaceX Hyperloop competition, the Elon Musk brainchild that challenges teams of college students to design and build high-speed pods. The Canadian team didn't win, but its second-place finish was good enough for Cadigan and Day to land jobs at another Musk startup, Neurolink.

There, the two engineers leveraged knowledge gained from the Hyperloop experience, for which they designed control boards and worked on data acquisition. Meanwhile, Noseworthy wrapped up an internship at Wind River, which led to a position there as a firmware developer. At the same time, Warren was in Silicon Valley working as an engineer at Apple.

All along, says Cadigan, they dreamed of launching their own tech company based around a more innovative PCB visualizer. As part of a capstone project, an independent research project for graduating seniors, they turned lessons from computer vision classes into a hypothesis that PCBs, as planar objects, would be wellsuited to augmented reality (AR) technology. "That wound up not being true, but it was enough to get us started," he recalls.

That start turned into a method for accelerating hardware development through faster debugging tools. The novel system highlights the nets on a board and captures and shares the metadata with other engineers, regardless of the native tool environment.

In 2018, a friend of Cadigan's happened to be attending the Del Mar Electronics trade show, where he met Mihir Shah. Shah was attending on behalf of Royal Circuits, a printed circuit board fabricator with factories in Northern and Southern California owned by his father, Milan. Prior to joining his father at Royal, Shah worked as an electrical engineer designing and validating boards at Tesla and Axon. He recalls the lengthy amount of time spent bouncing from screen to screen in the lab while debugging PCBs.

Ticking off the various instruments – the functional generator multimeter, spectrum analyzer, the PCB plus breadboard, oscilloscope, power supply, and PCB schematic screen – Shah says, "You have several different screens on your bench, and they all give different pieces of information that, while all relevant, are relevant to different people in the hardware development process – whether you are a firmware engineer or an EE or a technician. If you want to translate that info to others on your team, it's just another place to make mistakes and send the wrong file. So if you send someone a test instruction to probe these pads and send back the results on the oscilloscope or the DMM (digital multimeter), you get an email with 14 attachments, and you don't know what is necessarily referencing what."

And that leads to a lot of time and re-spins – Cadigan estimates the average number is six per design – and, of course, cost. Mihir, who saw the value of this potential workbench of the future, said he was immediately interested in becoming a customer. "I wanted to be able to click one net or component and know what it was and how it was connected. I thought it could be a competitive advantage for Royal."

After getting in touch with the four Canadian engineers, Mihir suggested they all meet up when the team was down in the Bay Area to interview with Y Combinator, the startup accelerator known for giving companies like Airbnb, DoorDash and Dropbox their start. In November 2018, YC passed, but according to Cadigan, just reaching the interview stage with a functional demo was validation they were on the right track.

During that same trip, the guys met with Mihir and Milan Shah. Mihir could not stop talking about how impactful and exciting that first meeting was. "We loved these guys. They were earnest, smart, and ready to build something great. My dad loved them. We decided to invest. We could guide them and introduce them to our customers." The first full system was rolled out in March 2019, and a few months later Mihir Shah joined as chief executive to help build the business and develop a strategy beyond the product itself. Royal Circuit Solutions and Advanced Assembly backed the venture with a reported \$850,000 equity investment.

Now called InspectAR Augmented Interfaces, the startup rounded out its vision. The strategy quickly evolved, the founders agree. "We first thought of overlaying designs directly onto the board as an incredible feat that would serve as the ultimate EE product," says Shah, "which is still the guiding principle. Though, as we started developing our product roadmap, we knew it would go way beyond that."

"We realized there was all these time savings," says Cadigan. "It could be a platform where people delegate work, where they need technicians or other people to help. There were so many remote collaboration possibilities. This became even clearer with Covid. You can walk someone through a design much faster. We didn't see that at first."

The InspectAR system can highlight any net, layer or component data on the board without accessing the related native files from the CAD tool directly, Shah says. "It's more intuitive to know where each signal goes. You know what each pin is, no matter which tool you use. And you get all the metadata in one place: pinouts, component datasheets, values, connected nets, and component locations." Overlays for innerlayers use a different color to highlight a trace from L1 to L4, for instance. "With InspectAR," Shah continues, "now, if I have a problem with an IC, I could call the vendor, and they could pour it into my lab. 'Try this; probe that,' and do it in minutes instead of days. It's tele-engineering." While Shah emphasizes the "most important element" is the ability to eliminate the need to constantly switch between printed schematics, EDA tools,

loose components, and the board, the coronavirus pandemic brings the full potential of InspectAR into clear view. "Say production is in China, but the engineer can't go over there, so they put InspectAR up, where everyone onsite can view it, and a remote collaborator can join the session and help resolve an issue.

The InspectAR software highlights nets and pulls up pin, component and other data, regardless of the ECAD system.

"Some folks do this kind of probing on Zoom, but it's hard to show what is being highlighted. Using InspectAR, it could be like you are sitting next to them in the lab. You can walk them through what you need to do. With Covid, the application of bringing contextual information into a single place is very exciting."

The InspectAR platform comes in various versions. A free single-user version is designed for hobbyists, and those who want to quickly get a feel for the technology. Users can get value out of inspectAR for free, with a library of "sponsored" boards from Digi-Key, Crowd Supply, SparkFun and more. With 2.0 coming out, the free version will also allow users to create projects for their custom PCBs designed in KiCAD and Eagle. At the professional level, a pay-per-project version has a small yearly fee for the engineering tool. Professional users can also take advantage of desk-top support (PC and Mac), along with support for more file formats (e.g., IPC-2581B from Altium and Cadence) and extended collaboration features. For a larger fee, the firm will build an on-device local version for onsite use for enterprise customers.

More than 1,000 users have signed up for the free tool and are enterprise customers in just a few months of being live, in all end-markets: military, aerospace, and so on.

"In two years, we want a larger free user base, and a good percentage converted to using the tool in some kind of professional capacity, whether a single engineer or **Luminovo**, an AI and machine-learning startup, has raised more than  $\in 2$  million in pre-seed financing to support its goal to redefine how PCBs are brought from concept to market.

Nano Dimension named Accelonix agent for the French market.

Safari Circuits selected a CheckSum ILS test system.

**Technica USA** named **TCT Circuit Supply** sales representative of EMC products.

Wise signed an agreement to use Plasmatreat's Openair-Plasma in its new Wonderwise 220 surface prep machine.

# **CA** People

ASYS named **Bob Drake** Southeast regional sales manager.

Bright Machines named **Steve Heinzen** business development director. He spent the previous 20 years in sales and marketing leadership roles at Neo Tech, Tandon Group and Flex.

Europlacer named John Perrotta president, global sales and services. He was president of Europlacer Americas for six years and has more than 30 years in SMT equip-

ment sales.

Inovar hired **Jeremy Grubb** as vice president of quality. He spent the past 12 years at L3Harris in supply chain, operations, quality and, most recently, was director of sup-

plier quality.

Libra Industries promoted Mike Lynch to director of quality assurance. He has been with Libra for more than 12 years.

Nordson announced **Joseph P. Kelley** as chief financial officer.

Specialty Coating Systems promoted **Tim Bender** (left, top) to president and CEO, replacing the retiring **Terry Bush** (bottom). Bender was named head of marketing in 2003 and joined the executive leadership team as vice president of sales and marketing in 2006.

VJ Electronix appointed Mark Clemons general manager. Former GM Don Naugler becomes director of technology.

WPG Americas named Jacqi Chase business development specialist. She spent 16 years as director of marketing for Sunburst EMS.

# **CA Briefs**

**3CEMS** added a Koh Young KY8030 3-D SPI.

AIM Solder named GR SYS Equipamentos Industriais distributor in Brazil.

**Cognex** named **Creative Electron** as a Partner System Integrator (PSI).

The ECIA said US export restrictions on many technologies to China, Russia, and Venezuela are "exceedingly broad" and have the potential for unintended consequences.

Japanese component suppliers are asking a US court to toss an antitrust suit filed by **Flex**, saying that it should be handled in arbitration.

**Foxconn** plans to build a joint IC packaging and testing plant in Qingdao, Shandong Province, China, as part of the company's efforts to enter the semiconductor industry.

**IEC Electronics** expects to finish construction on its new state-of-the-art electronics assembly plant this summer.

Integrated Test Corp. selected a Mirtec MV-7U Omni 3-D AOI.

Intervala acquired EMS provider Princeton Technology for an undisclosed sum.

**IPC** seeks papers for the High Reliability Cleaning and Conformal Coating Conference taking place Nov. 4–5.

Javad EMS installed a VJ Electronix Summit 1800i rework system.

Kurtz Ersa is offering Interflux's SelectIF 2040 and PacIFic 2009M VOC-free fluxes.

**Rochester Institute of Technology** recently installed a **Mirtec** MV-3 Omni AOI machine in its Center for Electronics Manufacturing and Assembly.

**Spectra-Tech** acquired five **Mirtec** MV-6 Omni 3-D AOI systems.

Synapse Electronique installed two Universal Instruments Fuzion Platform production lines in its Shawinigan, Quebec, EMS facility.

Variosystems acquired Solve Engineering for an undisclosed sum.

in a group," Cadigan says, outlining the company goals.

Currently it works with CAD tools from Altium, Autodesk Eagle, Cadence, and Kicad, and integrates with distributors like Digi-Key and Mouser. InspectAR is also adding integration with different lab tools, like an oscilloscope that connects to WiFi. "If that can be connected to the tool, it will be more powerful," Cadigan says.

InspectAR plans to launch rev. 2.0 of its signature product in about a month. The next revision performs 3-D object tracking, rotations to enable 3-D viewing at more angles, and scanning calibration. Another feature is new parsing technology. The bill of materials parser receives the component datasheets live, Shah explains. "For ondevice users, we can integrate local PLM and custom BoMs." A web connection is required for users who want this in real-time, although InspectAR is working with major parts distributors on caching, so the data will be present longer.

Other potential developments: smart work orders that communicate electronics knowledge bidirectionally, enabling interactive AR guides that can be distributed to individuals. "You can track that documentation and put it into your management software to make it useful for teams," Shah notes. An ECAD-agnostic mobile version could allow users phone access for viewing and determining a feature or a net without opening a PC.

In the meantime, the staff numbers 11 and is expected to double in 12 to 18 months. Shah is part of Autodesk's Technology Center program in San Francisco, while the rest of the staff is in Newfoundland. The team seeks sales staff, more software developers and "anyone who is excited about making augmented reality software for PCBs," says Cadigan, now chief product officer. (Day has become CTO, Noseworthy CIO and Warren COO.)

Asked whether the company will ultimately relocate to the Silicon Valley, Shah dismisses the idea. Sharing a photo of the company's idyllic workspace in St. John's – a wall of glass overlooking the waters of the Atlantic – he says the combination of location, engineering talent and relatively low overhead makes Newfoundland the perfect place to build the workbench of the future. (MB)

# NCAB Buys Bare Board Group

**BROMMA**, **SWEDEN** – NCAB Group signed an agreement to acquire 100% of the shares in Bare Board Group for \$12 million. BBG had revenue of approximately \$30 million in 2019.

"We are very happy to join forces with BBG," said Martin Magnusson, president of NCAB Group USA. "NCAB Group USA and BBG together will take on a leading position in the US PCB market. This brings additional value to our North American segment, with increased ability to offer our customers superior quality and service, as well as more volumes to our existing factories. BBG's supply chain management and factories are mainly located in Taiwan, which is a great supplement to our existing factory base and allows for more options in order to satisfy our customers' PCB demands in the future. We have the same value-driven organization and the same focus on giving our customers excellent quality and service." (CD)

# **Creation Technologies Acquires ATS**

**BOSTON** – Creation Technologies acquired Applied Technical Services, expanding Creation's manufacturing facilities and design centers operating across the US, Canada, Mexico, and China. No financial terms were disclosed.

"We are investing to broaden our capabilities and reach with the addition of the ATS team, who share our values of providing exceptional customer service and outstanding quality," said Stephen P. DeFalco, chairman and CEO, Creation Technologies.

The acquisition expands Creation's capabilities in the aerospace and defense, medical, and tech industrial markets. It adds locations in Everett, WA, and Hermosillo, Mexico, each offering three automated SMT lines, as well as automated through-hole, ICT, flying probe, and functional test capabilities. (CD)

#### EDITED by CHELSEY DRYSDALE

| WATCHING THE FALL?                                                                                                                                               |       |               |       |       |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------|-------|--|--|

| US electronics<br>equipment shipments                                                                                                                            | JAN.  | % CH/<br>FEB. |       | YTD%  |  |  |

| Computers and electronics products                                                                                                                               | -0.1  | 0.3           | -0.2  | 1.6   |  |  |

| Computers                                                                                                                                                        | 3.8   | 0.0           | -2.6  | -14.5 |  |  |

| Storage devices                                                                                                                                                  | 9.0   | -1.4          | -4.4  | 32.8  |  |  |

| Other peripheral equipment                                                                                                                                       | 2.8   | -1.2          | -0.4  | 9.6   |  |  |

| Nondefense communications equipment                                                                                                                              | -1.4  | -0.4          | 2.3   | 6.0   |  |  |

| Defense communications equipment                                                                                                                                 | -17.2 | 4.2           | 3.7   | -9.4  |  |  |

| A/V equipment                                                                                                                                                    | -10.0 | -4.5          | -13.4 | -31.1 |  |  |

| Components <sup>1</sup>                                                                                                                                          | 1.7   | -0.3          | -1.5  | 9.0   |  |  |

| Nondefense search and navigation equipment                                                                                                                       | 0.5   | -3.9          | -2.9  | -3.9  |  |  |

| Defense search and navigation equipment                                                                                                                          | -0.5  | -0.2          | 0.2   | 3.7   |  |  |

| Medical, measurement and control                                                                                                                                 | 0.9   | -0.9          | 0.7   | -2.2  |  |  |

| <sup>1</sup> Revised. *Preliminary. <sup>1</sup> Includes semiconductors. Seasonally adjusted.<br>Source: U.S. Department of Commerce Census Bureau. May 4, 2020 |       |               |       |       |  |  |

**US MANUFACTURING INDICES** JAN. MAR. APR. DEC. FEB. PMI 47.8 50.9 50.1 49.1 41.5 New orders 47.6 52.0 49.8 42.2 27.1 Production 44.8 54.3 50.3 47.7 27.5 Inventories 49.2 48.8 46.5 46.9 49.7 Customer inventories 41.1 43.8 41.8 43.4 48.8 Backlogs 43.3 45.7 50.3 45.9 37.8 Source: Institute for Supply Management, May 1, 2020

| KEY COMPONENTS                                                                                                                                                             |                   |                    |        |                   |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|--------|-------------------|-------------------|

|                                                                                                                                                                            | NOV.              | DEC.               | JAN.   | FEB.              | MAR.              |

| Semiconductor equipment billings <sup>1</sup>                                                                                                                              | 9.1% <sup>r</sup> | 17.8% <sup>p</sup> | 22.7%  | 26.6%             | 20.1%             |

| Semiconductors <sup>2</sup>                                                                                                                                                | -10.7%            | -5.4%              | -0.35% | 5%r               | 6.9% <sup>p</sup> |

| PCBs <sup>3</sup> (North America)                                                                                                                                          | 1.08              | 1.09               | 1.05   | 1.15              | 1.15              |

| Computers/electronic products <sup>4</sup>                                                                                                                                 | 5.50              | 5.47               | 5.45   | 5.49 <sup>r</sup> | 5.49 <sup>p</sup> |

| Sources: <sup>1</sup> SEMI, <sup>2</sup> SIA (3-month moving average growth), <sup>3</sup> IPC, <sup>4</sup> Census Bureau, <sup>p</sup> preliminary, <sup>r</sup> revised |                   |                    |        |                   |                   |

Hot Takes

- Worldwide IC unit shipments will fall 4% this year, the firstever back-to-back annual decline. And the overall memory market is expected to be flat. (IC Insights)

- Advanced packaging for data center servers, AI accelerators, and 5G infrastructure is a potential growth area in 2020. (TechSearch International)

- Semiconductor sales totaled \$104.6 billion during the first quarter, up 6.9% from 2019. (SIA)

- Tablet shipments fell 20% year-over-year to 24.6 million units during the first quarter. (IDC)

- Electronics now account for 40% of the cost of a new vehicle. (Deloitte)

- Taiwanese manufacturers said orders for electronic products in March increased 24%, compared to the same period last year. (Taiwan Department of Statistics)

- Nine EMS transactions took place in Q1. (Lincoln International)

- The smartphone output this year will slump 11.3% to 1.24

billion units. (TrendForce)

- Global PCB end-use demand was down 4.6% in 2019, and PCB output was \$68.3 billion, down 1.2% year-over-year. (TPCA)

- Worldwide PC shipments fell 8% year-over-year in the first quarter, the largest quarterly drop since 2016. (Canalys)

- Most US firms in China currently have no plans to relocate production to other parts of the country or abroad due to the coronavirus, but there is less certainty about the long term due to growing worries over US-China. (Pricewaterhouse Coopers)

- The global electronics adhesives market is projected to reach around \$14 billion by the end of 2027, growing at CAGR of 12.1% from 2020 to 2027. (CMI)

- Some 90% of component manufacturer representatives expect Covid to have a "serious to severe" impact on their business during the next two to three months. (ECIA)

# I Forgot a Work File. Will DFARS Mind if Someone Emails It to Me?

Working from home brings many Covid epiphanies.

AS I RELUCTANTLY get used to social distancing, wearing face masks in public and continually washing my hands, many "aha!" moments have occurred. These have been about the new realities of dealing with the global disruption from Covid-19, as well as the changes we will most likely live with once we've survived the pandemic, or at least the first round of it. In no particular order, they include:

Zoom, Zoom, ZOOM! I am not tech savvy or social media conscious, so it should be no surprise that three months ago I had never heard of Zoom. I know about it now! I spend a good portion of each day, including weekends, on a Zoom "call." At first it was family trying to connect from the various places they were hunkered down. But then I began receiving requests from customers and suppliers to schedule a Zoom meeting to discuss one or another thing. Zoom enables those working remotely to participate with the few still working out of their office or factory. Zoom is userfriendly, and unlike WebEx, easier for those working at home to manage.

What I find intriguing about the use of Zoom is how those working at home can put up a background picture or just talk with a blank screen to avoid those on the Zoom from seeing their cluttered kitchen or den. It certainly reduces potential embarrassment for some who work from home. But imagine, anyone can get a picture of a world-class manufacturing plant – or process line – or shelves of "inventory" for display so viewers think *that* is their plant. Oh, the potential here is limitless!

The little things! What did you leave in your office while working at home? Passwords, fobs, files with instructions to access some web account you only need to do once in a blue moon, all of which seem to happen during the pandemic. Many folks I have spoken with have had to go into someone else's desk to grab a file or password, then scan and email it to a coworker working at home. Many customers have found it difficult to get signoffs for purchase orders, as the key person working from home does not have access to some file or software to review or approve. Ditto financial managers, who are missing just one of the two factor authorizations needed to perform a task. Working from home works well for many, but some effort is needed to make it work for all.

PETER BIGELOW is president and CEO of IMI Inc.; pbigelow@imipcb. com. His column appears monthly.

NIST-800-Cybersecurity, *et al!* With everyone working remotely, who cares about cybersecurity? More than one person I know is working from home using a home PC running Windows XP or Windows 7, neither of which is still supported by Microsoft. Cybersecurity no no! Surprise! They cannot access some, if not most, of their company IT databases. But not to worry, there is *always* a workaround. Some take pictures of documents with their phone and text them to a coworker, who then uploads the photos into a file/document and then emails that file to a remote coworker. Even companies with the most robust IT infrastructure and resources to set up employees to work from home on company-supplied computers are cringing when the athome employee needs to print a document and does so on a non-secure printer or via a wireless device on their home (read: non-NIST-compliant) network.

I doubt when DFARS/NIST developed the various protocols outlined in the volumes of cybersecurity documents and requirements, they ever envisioned so many users working from remote locations. My guess is a zillion revisions to NIST-800 will be released soon. Possibly all the cellphone and cable companies will be required to comply to the NIST requirements. Can't wait to see how they accomplish that.

**Cubicle**, **oh cubicle**! The brainchild of some office architect in the 1960s, the art of the cubicle has been refined through the years. Today's office environment focuses on collaboration; the physical proximity allows us to bounce ideas off coworkers, interact with colleagues, and build a sense of camaraderie for the common, corporate good. Well, back to the drawing board! Manufacturers, service providers and commercial real estate brokers are discussing how to *separate* people, including enabling some to work from home, and others to split shifts to reduce interaction and promote social distancing.

The office of the future may look remarkably like the office of the past, with discrete offices and spreadout traditional desks that enable six feet between each employee. Equally shared workspace, where three people share a desk, but only one is in the office on a given day, may also become standard. Cafeterias or lunchrooms offer their own challenges and may need to undergo a social distancing redesign.

Shop floor elbow room! Like the office, many are looking at their manufacturing shop floor and rethinking how close process lines should be, or how to make a work "cell" appropriate for social distanc-

continued on pg. 19

# Marketing and the Post-Covid 19 World

Ramp the advertising programs and support them with content tied to sales efforts.

IN MY APRIL column, I discussed the communications strategies that were most important as Covid-19 began to change our working lives. This month, I look at communications strategies that *will* be most important as we resume the new normal working world. As I write this, the strategy for reopening businesses is just being formulated. From everything I've seen reported, it appears the strategy will be a rolling relaxation of restrictions, which means geographic advantages for companies in places that either had minimal infection rates or have successfully flattened their curves. Roll-

ing increases of restrictions are also likely if a region starts to see new spikes in infections.

From an electronics manufacturing services (EMS) provider perspective, what does that mean? First, consider what Covid-19 has done to this business sector. Many EMS providers remained operational at some level thanks to product mixes that included essential products that support infrastructure or medical needs. However, even those companies typically are working at reduced levels and have experienced employee angst about virus risk.

Customers with nonessential product are in some cases cutting forecasts dramatically and in other cases will have a lot of pent-up demand. Those trends depend on whether the product is something buyers have simply been waiting out the quarantine to purchase or will likely not purchase for months after the quarantine ends. When you overlay today's trends on a post-Covid-19 world, it translates to manufacturing constraints, supplychain constraints, plus pockets of oversupply. If a large part of the US gets back to work by May 1, it is likely that pent-up demand will continue to be a factor. If the quarantines in place in mid-April extend through May in a large part of the country, it is hard to predict what the demand landscape will look like. Datacom, industrial and medical products will likely remain strong, but consumer demand will drop dramatically.

The international picture is also a factor. While most of Asia and parts of the EU are either back to work or planning to get back to work shortly, Mexico is just starting to feel the impact of the virus, and the inefficiency of Mexico's state governments in determining essential businesses is going to impact EMS

"Focus social media, web, advertising or whitepaper content on how you solved supply-chain challenges."

facilities. Companies with good Mexican legal counsel and strong relationships with their local maquiladora associations are likely to do better than those without those relationships. The global supply chain remains imbalanced, which means logistically that transport chains are also imbalanced. Even if a manufacturer can produce, it may not be able to get that product from point A to B as quickly as its customer needs. OEMs also cannot get their products from point A to B as quickly as their customers may need.

From a marketing perspective, it becomes impor-

tant to get into the mind of prospects and customers. The scenario I've just laid out has created frustration and destroyed every 2020 forecast and budget in existence. It also shows the weak spot of supplychain consolidation. Sourcing strategies that have geographic variety are now more relevant. So, while little will change immediately, sourcing teams are likely compiling lessons learned right now and formulating new sourcing strategies. As a result, EMS marketing activities should align with the lessons-learned mentality that

sourcing teams are likely to embrace. Here are my thoughts on marketing strategies most likely to work:

Prospects that evaluated your company but elected to stay with current suppliers are lowhanging fruit. Sourcing teams aren't going be excited about jumping on planes for a few months. Consequently, companies they've already evaluated may be the first they consider if they need to shift production due to capacity constraints at their current suppliers or decide to begin moving production from China. Sales teams should build relationships by providing educational content on recent customer success stories in the areas of project transfers, mitigating supply-chain constraints or ability to support unanticipated surges in demand. Workplace infection mitigation strategies should also be highlighted. Also, determine if there is a way to support virtual facility audits, should a prospect that has previously toured want to take a next step without travel.

LinkedIn, blogs, article placements and advertising should expand. Trade shows are going to be SUSAN MUCHA is president of Powell-Mucha Consulting Inc. (powellmuchaconsulting. com), a consulting firm providing strategic planning, training and market positioning support to EMS companies and author of Find It. Book It. Grow It. A Robust Process for Account Acquisition in Electronics Manufacturing Services: smucha@powellmuchaconsulting. com

unlikely for months. Even if third-quarter trade shows are held, many companies may be restricting business travel to discretionary events, so attendance will be down. At the same time, OEMs will be reevaluating sourcing strategies. From a marketing standpoint, it is important to have strong, targeted messaging reaching as much of the market as possible. Companies with limited budgets can use social media, blogs and PR to get out that message. However, advertising is likely a good investment for the rest of the year because it acts like a road sign directing readers to your more detailed educational content.

Messaging matters. In a stable market with little differentiation among suppliers, decisions get made on price. In a chaotic market, decisions get made based on a sourcing team's perception of which company is most likely to address the challenges their team is facing. The biggest challenges today are getting projects transferred quickly, managing supply-chain constraints, addressing spikes in demand, supporting legacy product, staying operational and addressing logistics challenges. Companies with geographically dispersed facilities and those with facilities in areas that are remote enough to have not seen infection have a competitive advantage. Companies whose social media, web, advertising or whitepaper content discusses how they have solved some or all of those challenges, or highlights the geographic

resiliency of their facility locations, are going to be more competitive than those talking about capacity or equipment.

Transparency still matters. It is still important to be honest in communications about operational constraints with employees, customers and prospects. Marketing messages shouldn't overstate a company's ability to deal with regional constraints. In situations where constraints exist, it can be helpful to discuss a company's ongoing efforts to restart production as quickly as possible. Enhance customer retention by helping them understand what is being done to negotiate reopening with local governmental authorities, how furloughed employees are being retained, what infection mitigation practices are in place in each facility and how project recovery activities will be handled. In the absence of information, sourcing teams will develop their own recovery plans.

Covid-19 has caused massive disruption around the world. However, chaos always opens the door to opportunity for those who look for it. Start planning and executing post-Covid-19 marketing strategies. This will be an educated sell that requires content that addresses how an EMS provider is going to solve common challenges. Consequently, marketing programs that work will have detailed content backing up whatever advertising is done and strong linkage to sales efforts.

EOS/ESD Association, Inc. 7900 Turin Rd., Bldg. 3 Rome, NY 13440-2069, USA PH +1-315-339-6937 • Email: info@esda.org • www.esda.org

WE STAND TOGETHER

YOUR PARTNER IN SOLDER ASSEMBLY MATERIALS

AIM's worldwide technical support network of IPC certified engineers assists customers in obtaining optimal results in local time and local language.

AIM's commitment to ongoing research and development enables the company to develop innovative solutions for the manufacturing challenges of tomorrow.

AIM facilities are IATF 16949 and ISO 14001/9001 certified, ensuring sustainable, reproducible results around the globe.

# **AIM** Global Solder Solutions

www.aimsolder.com | info@aimsolder.com

# PCERCHO

# **Recent Chats:**

Teresa Huber

on EMS

Greg Papandrew Better Board Buying

Sebastian Schaal

on Al/Machine Learning in Electronics Manufacturing

upmg.podbean.com

# The PCB Podcast

# Your PCB Supplier Was Acquired. What Now?

Understand what the transaction means for customers.

YOUR PCB SUPPLIER has been acquired. Will this acquisition benefit you as a board buyer? Or will it lead to higher prices and a reduced level of service?

The answer may depend on how you react.

Vendor acquisitions can cause supply-chain disruptions, especially when the acquiring firm has a competing product line. Few PCB buyers seem to understand the real economics involved, or why they happened in the first place and what it means to them as customers.

Acquisitions usually fall into two categories: Either the acquiring firm buys the present customer base and its revenue stream, or it acquires some leading-edge or dissimilar technology of the acquired supplier – like a rigid supplier acquiring a flex manufacturer, for example. Either way, the goal of the acquiring firm is to catapult its sales efforts.

Interestingly, PCB suppliers that both manufacture and broker – whether in the US or abroad – may build boards for one another *and* broker from each other. Many board buyers don't realize how much overlap there is among manufacturers.

And that means, more than likely, when a similar supplier buys another, the acquisition is an attempt to grab a greater share of the market, rather than to accelerate an innovation strategy.

For the customer, the question is will they benefit? In practice, the relationship with the supplier and the level of service received is likely to change. What should you do to protect your business?

You should oversee your supply chain, not your supplier. While you may not notice changes in your relationship with the acquired vendor right away, take a close look at your PCB purchasing process. Don't wait to be visited by the new supplier team, especially if the acquired firm was a big part of your PCB spend. Request a meeting sooner rather than later. Pay attention to how receptive the new supplier is to the meeting and be ready to ask many questions to get the lay of the land.

Try to ascertain where your orders stand with the larger entity. What often happens when a larger supplier swallows a smaller competitor that builds similar product is customers immediately become smaller fish in a bigger pond. What was 5% before may now be only 0.5%. Ask the new entity what percentage your sales represent for them. Bigger is better.

Will you still be considered a target account for the larger vendor? Will the potential for superior PCB buying power of the large entity offset your company's (potentially) reduced significance?

Realistically, you will have less leverage on pric-

ing and service. In fact, the newly enlarged supplier may even raise prices to politely shed customers no longer seen as desirable.

Plan on personnel changes happening after a merger, so ask now how the new vendor intends to ensure a smooth customer service transition. The support staff you've worked with for years may be laid off to avoid duplication of costly services. The supplier's sales representatives may now operate under a different incentive structure that makes their relationship with you less important. Or sales reps may be let go.

Review any written agreements you have with the supplier and those with your customers. Do they contain a clause about changing possible subcontractors? Once a supplier is acquired, the new company is likely to try to move your business to PCB manufacturing locations that support *its* business operations, not necessarily to those best for your orders. Because of your customers' specific requirements, let the new vendor know which orders can't be moved and get it in writing that they will comply.

Also, update and review whether the new entity can maintain the nondisclosure (NDA), hold harmless, and service level agreements you require. Are payment terms the same? Delivery times? What about the RMA process? Does the new entity have a different warranty policy? Who is in charge of quality? And be sure to give them a copy of your most recent PCB fabrication spec. (If you don't have a fab spec, make it a priority to create one.)

In addition, develop a Plan B, especially if both vendors were supplying your company PCBs prior to the acquisition. Instead of two companies competing for your orders, you now have only one vendor who may not be as motivated to remain price-sensitive on your PCB orders.

Reach out to alternative PCB vendors for quotes, as they may be eager to give you price breaks and offer you a higher level of service, regardless of your annual PCB buy. At the very least, having an alternate source for your PCBs gives you more leverage with your new, larger vendor.

If the acquisition experience is not a good one for your company, cut the supplier loose by slowly migrating business elsewhere. Seek out other manufacturers. You can also bypass the broker altogether and deal directly with offshore manufacturers. That is now easier than ever before.

Either way, being prepared now will protect your PCB purchasing in the future.

### GREG

PAPANDREW has more than 25 years' experience selling PCBs directly for various fabricators and as founder of a leading distributor. He is cofounder of Better Board Buying; greg@ boardbuying.com.

# The Nuts and Bolts of a Via Padstack

Or why aspect ratio rules all.

THE HUMBLE VIA comes in many flavors. By connecting one layer of a conductor pattern to another, vias have connected the world. My career has depended on them as part of the hardware I used to design for others to use. A foundational innovation in electronics brought plated through-holes to the masses. As a leap forward from wire-wrap technology, multilayer printed circuit boards put a "mainframe" in each of our pockets almost overnight.

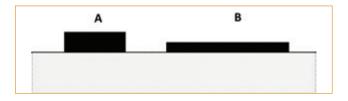

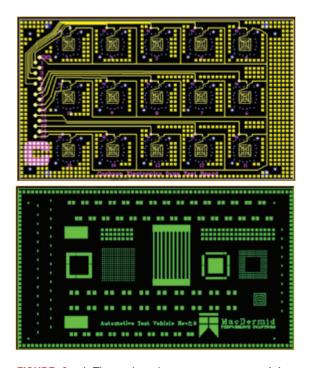

From the first plated through-hole to the latest, the trend is to support higher-density interconnect. The key driver in plating holes is the aspect ratio, the hole's width relative to its depth. For a through-hole, the depth is the thickness of the PCB. Most reputable fabricators can handle a 10:1 ratio, such that a common 0.062" board thickness will require a minimum finished hole size 0.006" (FIGURE 1).

Finished hole size is just what it says on the tin.

The initial drill will be one- or two-thousandths of an inch larger than the finished size to account for the thickness in the copper "barrel." The barrel is created by drilling throughholes and electroplating the top and bottom of the board prior to etching away the circuit pattern. There are two com-

plete sheets of copper of a starting thickness. As those are plated up, the prepared holes get their plating. That is all the copper that is added to form the barrel. Other protective layers come later.

The point is the optimum amount of barrel wall thickness depends on the outer layer geometry of the PCB. Trace width and especially airgap depend heavily on the thickness of the copper on the outer layers. Most of the time, there is a different set of rules for inner- vs. outer layers in terms of trace width and space. Up to a point, a larger hole will be easier to plate. As the smaller holes approach maximum aspect ratio, the plating must be more aggressive. Pressing on the factory capabilities inevitably leads to more X-outs. As yield drops, unit prices rise.

If board density permits, a 0.013" hole with a 0.25" capture pad is the sweet spot for low-cost PCBs. This would have good current capacity but could be

too much a discontinuity for a high-speed link. In that case, a 0.008" finished hole through a 0.018" pad is a good compromise and a go-to size for most plated through-hole designs. While inches were used, for the most part expect the metric system to apply.

With a solid via plan, the user can influence what to do when a via is not connected on a layer. I've been told a plated pad on the no-connect layer could expose the signal to magnetic coupling when the vias share an opening in the ground plane. I've also been told the extra annular ring helps anchor the via's barrel. That little extra copper that became the barrel could use those the same way a 55-gal. barrel has ridges. (I write gallons because "208.198 liters?")

Live a little. When a layout can afford to spread out on the top layer, it is a chance to get to a useful routing grid. Consider the number of channels that will route between each via. While it is tempting to

pair each via to the

SMD pad, optimiz-

ing the fan-out at the

device can help at the

connector end. A row

of vias will create a

slot in the ground

plane. Those who

simulate circuits like

that are apt to provide

some guidance if you

ask. If not them, then

the Federal Commu-

nications Commission

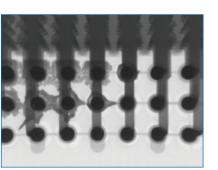

FIGURE 1. Ten layers of technology.

might like a word. Typically, the start and endpoint vias are the only ones you get with a high-speed bus. Slick fan-out will uncross P/N disagreements and get each member to an agreeable latitude to route to the receiver pin. Space around the signal via can become a coax in the z-axis by surrounding the via with three ground vias. This extreme care is normal when dealing with RF. Data rates of 2.5Gb/s deserve that kind of care as well. We want to avoid vias, but if we're doing them, we're doing them right.

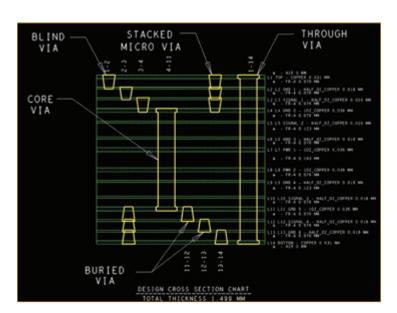

Blind, buried, microvias – now what? Freedom from the tyranny of through-hole PCBs happened (to me) around the turn of the century. Optical gear in the 10Gb/s space was competitive and constrained by

continued on pg. 19

JR. is a career PCB designer experienced in military, telecom, consumer hardware and, lately, the automotive industry. Originally, he was an RF specialist, but is compelled to flip the bit now and then to fill the need for highspeed digital design. He enjoys playing bass and racing bikes when he's not writing about or performing PCB layout. His column is produced by Cadence Design Systems and runs monthly

JOHN BURKHERT

# PCB Design Starts with the Materials, but Choosing is Tougher than Ever

A call for performance-centric materials specifications.

THE COMBINATION OF rising performance expectations and intense commercial pressures means choosing the right substrate materials for new-product designs is more important than ever. A wider selection of materials, with more finely nuanced properties, increasingly complicates making the "right" choice. Help is available from suppliers and industry bodies. But designers can also help themselves by being more willing to share information with their suppliers.

As PCB industry veterans, we know well the board is typically the last part of the project specified when a new product is designed. On the other hand, it's the first item needed when serious development begins. Designing the circuitry to go on the PCB obviously gets most of the attention, but the substrate itself is usually the lowest priority in engineers' minds. When the time finally comes to consider it, teams will often simply default to the same materials used previously. As performance demands imposed on successive product generations continue to intensify, and factors such as conductive anodic filament (CAF) formation that seriously affect reliability become more critical, this approach is increasingly unsatisfactory.

As the industry has come to understand more about how the substrate properties influence performance and reliability under various operating conditions, so the number and diversity of material types available has increased. In the past there were only a handful of options open to designers. Today, international specifications offer over 100 different material categories to choose from. Designers, understandably, struggle to connect the specifications with the properties sought. It doesn't help that these specifications are usually based on chemical composition. As the breadth of choice on offer continues to increase, it's almost impossible for electronics engineers to relate to them. I have been calling for some time for the industry to move to performance-centric specifications that are easier for engineering communities to interpret.

Getting help is essential, because struggling alone risks underspecifying or overspecifying the material for the application at hand. Neither is good: underspecifying risks the product coming up short in a way that could be beyond any realistic remedy. Overspecifying, to be "on the safe side," can be commercially disastrous in ultra-competitive markets such as consumer technology. The chosen materials also need to be readily available in any location globally where the product is to be manufactured. Some resins, for example, are only available in certain domestic markets and are difficult to procure elsewhere.

So, what to do? Qualifying or testing materials helps to understand their performance and properties but is expensive and time-consuming for companies to undertake independently. Pooled testing, where groups of companies get together to do specific tests and share the results, is one response. Also, the HDP User Group (hdpug.org) has several active programs including the Lead-Free PWB Materials Reliability project, which is currently in phase 6. I have run various phases of this project. It benefits from panindustry participation and has established a comprehensive set of analyses that cover Dk and Df, CAF, thermal stress, and other tests on standardized test coupons. Ventec has contributed several materials to this program, including one of the materials in the latest phase 6 tests.

Designers can also take advantage of another emerging trend among suppliers, which is to present carefully curated sets of materials for specific application areas. Our material guides, for example, bring together products with properties suitable for automotive or aerospace and further subdivide them according to target applications and operating environments, such as under-the-hood or in-cabin. In this way, suppliers effectively contribute their expertise to help customers short-list products that can meet their requirements. This helps by simplifying and accelerating selection, narrowing the focus to materials that are fundamentally suitable.

Helpful though this is, as suppliers we often need designers to express their requirements directly if we are to provide the right material for the right task. During my time in the industry, I have been involved in a few cases where large OEMs have been too sparing with information, particularly about the intended application and operating environment, and ultimately were obliged to recall large numbers of units from the field. With just a little more willingness to share information, the problem could have been avoided, rather than remedied at high financial and reputational cost.

While it's understandable for any OEM to be wary of sharing information about its IP and product strategies, cases like these highlight the value of trust between OEMs and their suppliers. I have called before for greater openness and trust. As materials selection becomes more complex and, at the same time, more important to get right the first time, there is more to gain by finding ways to be open and more to lose by keeping traditional barriers in place. ALUN MORGAN is technology ambassador at Ventec International Group (ventec-group. com); alun.morgan@ ventec-europe.com.

# Can Rigid-Flex Have Different Layer Counts in Different Areas?

Yes, but there are performance and cost tradeoffs.

YOU HAVE STARTED a new design. The chassis is defined, and you are thinking about how everything could be connected. Unlike the past, you are thinking about the interconnect strategy early in the design process, rather than at the last minute. Now you must decide what will be connected as an integrated rigidflex and what might need to be done separately. So many design options are available right now. Here is where the question comes up: What if my layer counts are not consistent everywhere?

When faced with this, don't worry. Rigid-flex allows us to design in almost any configuration. Each has performance and cost tradeoffs. Let's review few of the more common design styles.

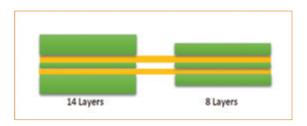

Combo board. This design joins two processor boards. However, the left board has more functionality and therefore requires more layers. What to do? You could make the left board 14 layers and the right board eight layers, as you may think that would save money (FIGURE 1). That is not the case, however. In fact, it is more expensive to leave it as 14 layers on one side and eight layers on the other. This is because circuits are built in a panel format, and the material for all 14 layers exists in all areas. Tooling is developed to remove material where it isn't wanted. Thus, you pay for all the material and then pay to have it selectively removed. In addition, the eight-layer side needs to be drilled and plated first. Then the rest of the 14 layers get added, drilled and plated again. This means paying for double processing. To avoid this cost, we recommend both boards have all the material for 14 layers. If the layers aren't needed, add nonfunctional pads or extra planes. Who doesn't like another ground plane?

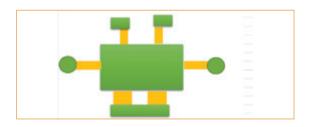

The octopus. Maybe you have a design with a main processor/backplane board, with arms coming off in many directions (FIGURE 2). The main board has 12 layers. There are flex arms, each with flex layers terminating at an I/O connector end. At these ends, you only need four to six layers to pin it out. You might stop there, thinking it will be lower cost if no material is added where it is not needed. Again, it is cheaper to leave the extra material there.

Sometimes, however, you may have a constraint. In some cases, there is not enough space in the box. Alternatively, maybe the connector you need only comes with shorter pins. If that is the case, you may need to reduce the layer count. Don't fear. It can be done; it just takes extra processing. Your supplier can help you with the design to minimize cost impacts. The overlapper. In this type of design, multiple flexes need to exit the main board in the same x-y plane (FIGURE 3). Their terminations overlap or sit on top of each other in a staggered fashion.

This is a bit more complex, and there is no way to make all the rigid ends the same. In this type of design, the main portion of the board needs at least two more layers than the two rigid tails combined. This is because this type of board is constructed as two separate boards: one for the top and one for the bottom tail. Then, they are laminated together between additional rigid layers. These additional rigid layers serve two purposes. First, they provide for additional routing in the main board to connect top and bottom. Second, that material creates a pouch around the previously fabricated tail ends to protect them for the remainder of the circuit fabrication. In

FIGURE 1. The combo design varies the number of layers in each board.

FIGURE 2. A board with arms coming off in many directions, like an octopus, is less expensive to build if any extra material is left intact.

FIGURE 3. If multiple flexes need to exit the main board in the same x-y plane, the main portion of the board needs at least two more layers than the two rigid tails combined.

is senior field applications engineer at TTM Technologies (ttm.com), vice chairman of the **IPC Flexible Circuits** Committee and co-chair of the IPC-6013 Qualification and Performance Specification for Flexible Printed Boards Subcommittee; nick. koop@ttmtech.com. He and co-"Flexpert" **MARK FINSTAD** (mark.finstad@ flexiblecircuit. com) welcome your suggestions. They will speak at PCB West (pcbwest.com) in September.

NICK KOOP

## THE FLEXPERTS

this case, we must have more layers at the main board than we have at the tails. In these types of designs, ENIG is a preferred final finish, rather than solder.

There is a way around this if you revisit how you get from point A to point B. If you have space, you can jog one of the flexes around the rigid section of the shorter tail, and then back down to your longer termination end (**FIGURE 4**). In this way, all three rigid boards have the same layer count. This significantly reduces material and process cost. It also eases assembly.

Several variants on this exist where the flexes may need to overlap but terminate in different areas. Provided the rigid ends terminate with the same material sets, the impact to the unit cost can be managed.

All these options can be achieved, but each comes with a distinct cost. Select a design that gives all the connectivity you need without incurring unnecessary premiums.

FIGURE 4. By routing one of the flexes around the rigid section of the shorter tail, all three rigid sections can be the same layer count.

Once again, congratulations for thinking about the circuit options early in the design phase. This is where you can get the most performance and functionality and the lowest cost. Remember less is not always better.

#### ROI, continued from pg. 12

ing. Firms are looking at redeploying staff to second or third shifts to reduce the number of people in close quarters. At least one manufacturing engineer I know has been tasked with redesigning the manufacturing operation so people can be six feet or more apart. He claims that will be a colossal logistical endeavor based on the size and complexity of equipment to be moved. Others are talking about plexiglass "walls" between machines, much like can be seen today at grocers, to separate people. Like the office, the shop floor will look different and may expand as social distancing requires. The past few months have impacted everyone. However, it looks more and more like the impact is just beginning, and we all need to rethink how we do business, from where, and how close to our coworkers. The lasting change from Covid-19 may not be how many contract the disease, but how we all recalibrate our day-to-day life at home and at work going forward.

#### Designer's Notebook, continued from pg. 16

form factor. Chromatic dispersion along the fiber was a problem the company was solving using a 0.5mm pitch device. This is the point where the usual via can't help.

The beauty of a microvia (FIGURE 2) is it can be used within the SMD pad. Precious space that would be taken by fan-out vias can be used for more components. Via-in-pad technology is mainstream for RF and digital alike. Shorter inductive loops are possible for the decoupling capacitors using via-in-pad technology. Using a finish of ENIG (electroless nickel immersion gold) is common because it improves flatness. A flat pad provides a more consistent solder joint. Power devices, or anything with a ground pad, benefit from microvia-in-pad solutions.